Altera Low Latency Ethernet 10G MAC User Manual

Page 54

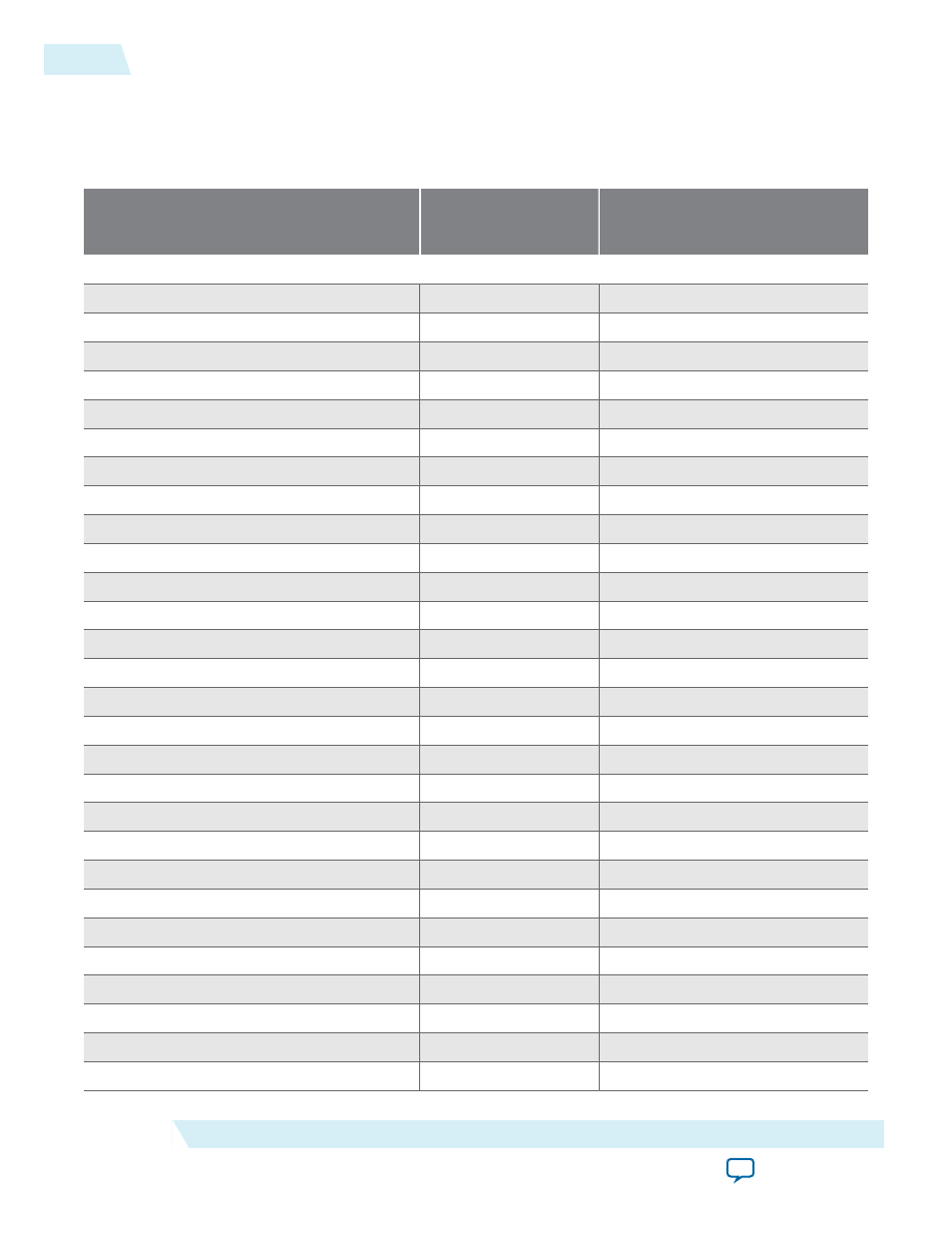

Mapping 10-Gbps Ethernet MAC Registers to LL Ethernet 10G MAC Registers

Use this table to map the legacy Ethernet 10-Gbps MAC registers to the LL Ethernet 10G MAC registers.

Table 4-2: Register Mapping

Register Names (10-Gbps Ethernet MAC)

Offset

(10-Gbps Ethernet MAC)

Offset

(LL Ethernet 10G MAC)

MAC TX Configuration Registers

TX Packet Control

1000

020

TX Transfer Status

1001

Not used.

TX Pad Insertion Control

1040

024

TX CRC Insertion Control

1080

026

TX Packet Underflow Count[31:0]

10C0

03E

TX Packet Underflow Count[35:32]

10C1

03F

TX Preamble Pass-Through Mode Control

1100

028

TX Unidirectional

1120

070

TX Pause Frame Control

1140

040

TX Pause Frame Quanta

1141

042

TX Pause Frame Enable

1142

044

TX PFC0 Pause Quanta

1180

048

TX PFC1 Pause Quanta

1181

049

TX PFC2 Pause Quanta

1182

04A

TX PFC3 Pause Quanta

1183

04B

TX PFC4 Pause Quanta

1184

04C

TX PFC5 Pause Quanta

1185

04D

TX PFC6 Pause Quanta

1186

04E

TX PFC7 Pause Quanta

1187

04F

TX PFC0 Hold-off Quanta

1190

058

TX PFC1 Hold-off Quanta

1191

059

TX PFC2 Hold-off Quanta

1192

05A

TX PFC3 Hold-off Quanta

1193

05B

TX PFC4 Hold-off Quanta

1194

05C

TX PFC5 Hold-off Quanta

1195

05D

TX PFC6 Hold-off Quanta

1196

05E

TX PFC7 Hold-off Quanta

1197

05F

TX PFC Enable

11A0

046

4-2

Mapping 10-Gbps Ethernet MAC Registers to LL Ethernet 10G MAC Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC