Unidirectional control registers, Unidirectional control registers -12 – Altera Low Latency Ethernet 10G MAC User Manual

Page 64

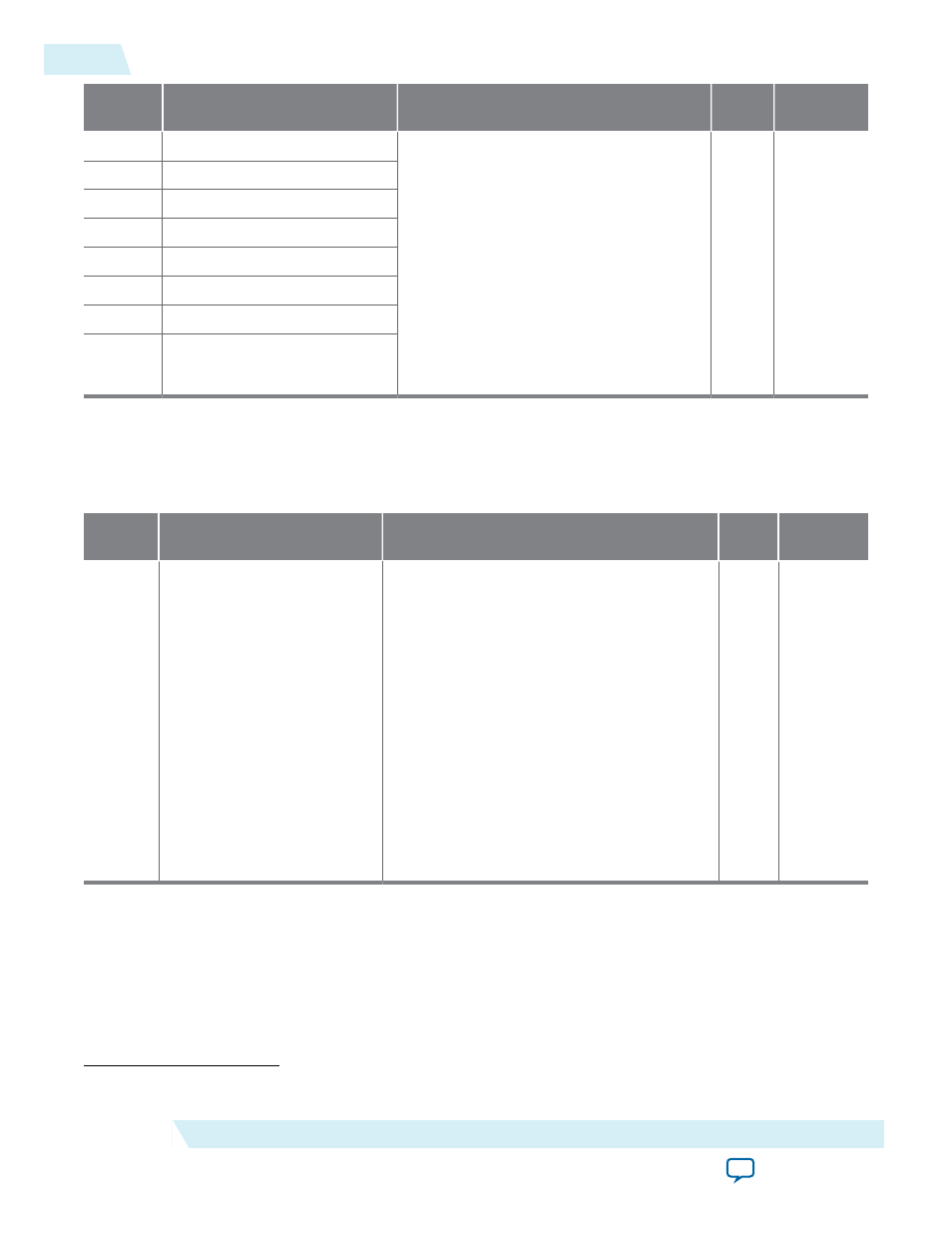

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0058

pfc_holdoff_quanta_0

(5)

Specifies the gap between two consecutive

transmissions of XOFF pause frames in unit

of quanta, 1 unit = 512 bits time. The gap

prevents back-to-back transmissions of

pause frames, which may affect the

transmission of data frames.

• Bits 15:0—

pfc_holdoff_quanta_

n[15:0]

specifies the gap for priority

queue n.

• Bits 31:16—reserved.

Configure these registers before you enable

the MAC IP core for operations.

RW

0x1

0x0059

pfc_holdoff_quanta_1

(5)

0x005A

pfc_holdoff_quanta_2

(5)

0x005B

pfc_holdoff_quanta_3

(5)

0x005C

pfc_holdoff_quanta_4

(5)

0x005D

pfc_holdoff_quanta_5

(5)

0x005E

pfc_holdoff_quanta_6

(5)

0x005F

pfc_holdoff_quanta_7

(5)

Unidirectional Control Registers

Table 4-8: Unidirectional Control Registers

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0070

tx_unidir_control

(6)

• Bit 0—configures unidirectional feature on

the TX path.

0: Disables unidirectional feature.

1: Enables unidirectional feature.

• Bit 1—configures remote fault sequence

generation when unidirectional feature is

enabled on the TX path.

0: Enable remote fault sequence generation

on detecting local fault.

1: Disable remote fault sequence generation.

• Bits 31:2—reserved.

Configure this register before you enable the

MAC IP core for operations.

RW

0x0

(6)

This register is used when you turn on Enable unidirectional feature. It is reserved when not used.

4-12

Unidirectional Control Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC