Altera Low Latency Ethernet 10G MAC User Manual

Page 59

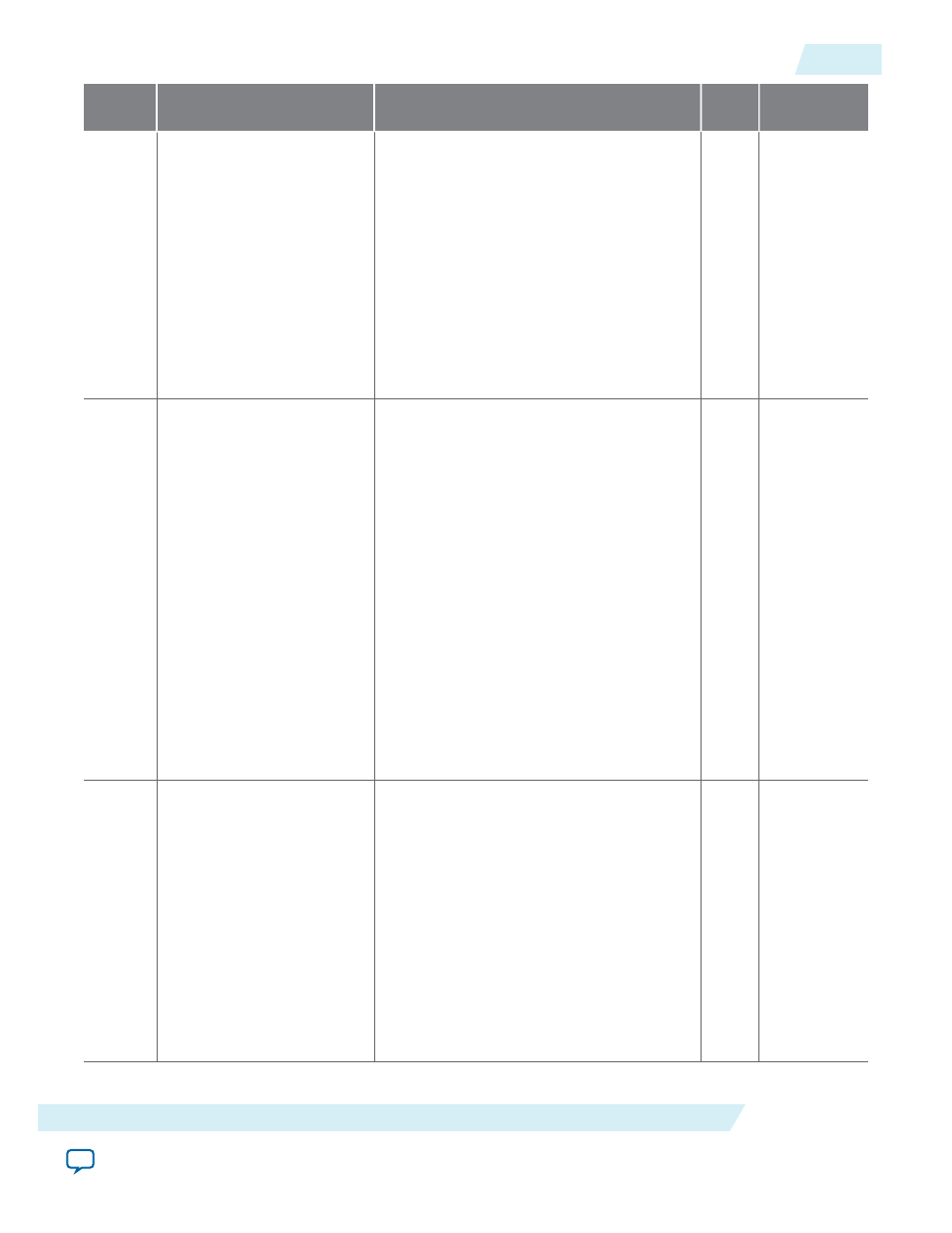

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0022

tx_transfer_status

The MAC sets the following bits to indicate

the status of the TX datapath.

• Bits 7:0—reserved.

• Bit 8: TX datapath status.

0: The TX datapath is idle.

1: A TX data transfer is in progress.

• Bits 11:9—reserved.

• Bit 12: TX datapath reset status.

0: The TX datapath is not in reset.

1: The TX datapath is in reset.

RO

0x0

0x0024

tx_pad_control

• Bit 0—padding insertion enable on

transmit.

0: Disables padding insertion. The client

must ensure that the length of the data

frame meets the minimum length as

required by the IEEE 802.3 specifications.

1: Enables padding insertion. The MAC IP

core inserts padding bytes into the data

frames from the client to meet the

minimum length as required by the IEEE

802.3 specifications.

When padding insertion is enabled, you

must set

tx_crc_control[]

to 0x3 to

enable CRC insertion.

• Bits 31:1—reserved.

Configure this register before you enable the

MAC IP core for operations.

RW

0x1

0x0026

tx_crc_control

• Bit 0—always set this bit to 1.

• Bit 1—configures CRC insertion.

0: Disables CRC insertion. The client must

provide the CRC field and ensure that the

length of the data frame meets the

minimum required length.

1: Enables CRC insertion. The MAC IP

core computes the CRC field and inserts it

into the data frame.

• Bits 31:2—reserved.

Configure this register before you enable the

MAC IP core for operations.

RW

0x3

UG-01144

2014.12.15

TX_Configuration and Status Registers

4-7

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation