Altera Low Latency Ethernet 10G MAC User Manual

Page 84

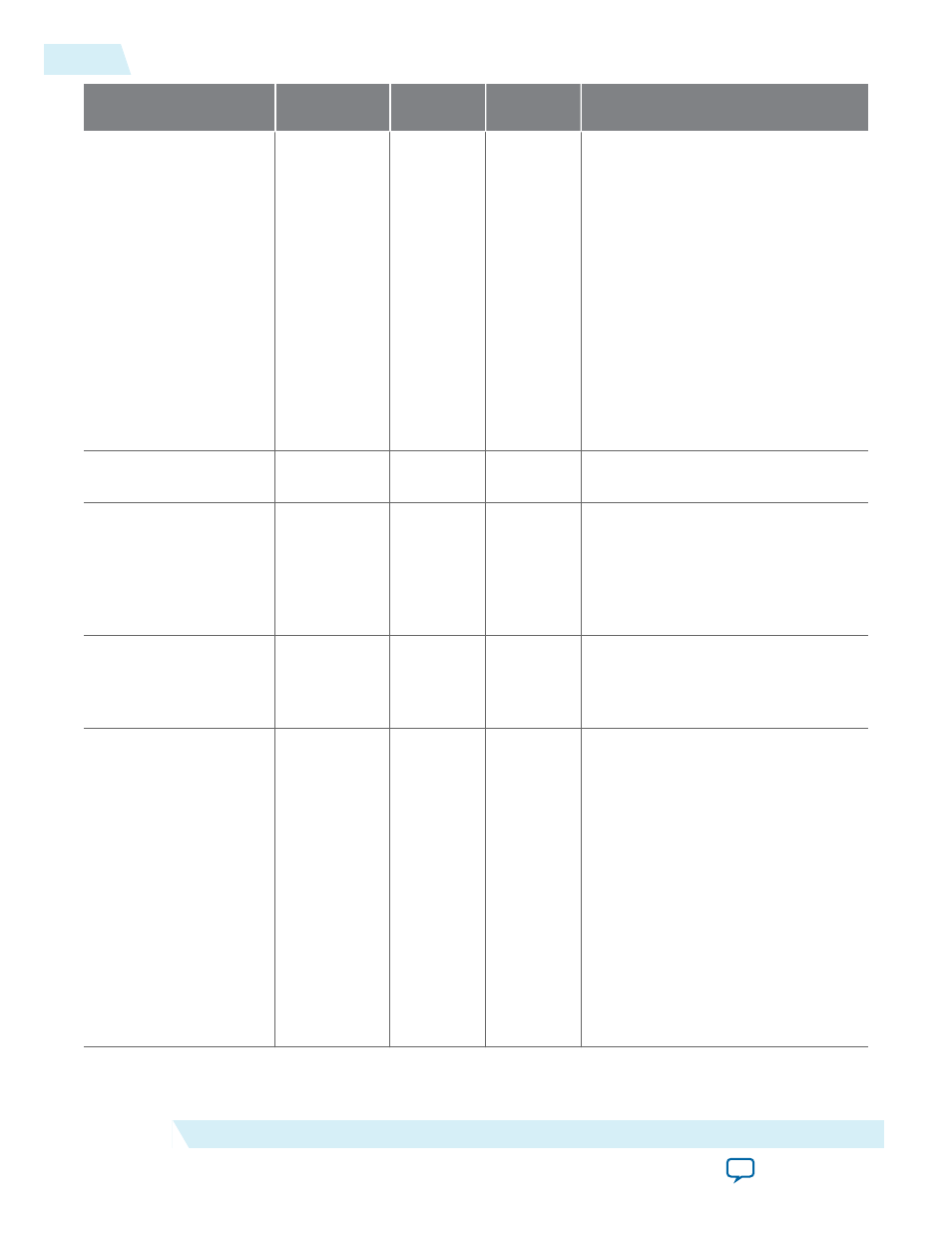

Signal

Operating

Mode

Direction

Width

Description

tx_156_25_clk

10G, 1G/10G,

10M/100M/

1G/10G

In

1

156.25-MHz clock for the MAC TX

datapath when you choose to

maintain compatibility with the 64-

bit Ethernet 10G MAC on the

Avalon-ST TX data interface or

XGMII. This feature is not available

when the Enable 10GBASE-R

register mode is enabled.

Altera recommends that this clock

and

tx_312_5_clk

share the same

clock source. This clock must be

synchronous to

tx_312_5_clk

.

Their rising edges must align and

must have 0 ppm and phase-shift.

tx_rst_n

All

In

1

Active-low reset for the MAC TX

datapath.

rx_312_5_clk

10G, 1G/10G,

10M/100M/

1G/10G

In

1

312.5-MHz clock for the MAC RX

datapath when the Enable

10GBASE-R register mode is

disabled. You may use the same

clock source for this clock and

tx_

312_5_clk

.

rx_xcvr_clk

10G

In

1

322.265625-MHz clock for the MAC

RX datapath when the Enable

10GBASE-R register mode is

enabled.

rx_156_25_clk

10G, 1G/10G,

10M/100M/

1G/10G

In

1

156.25-MHz clock for the MAC RX

datapath when you choose to

maintain compatibility with the 64-

bit Ethernet 10G MAC on the

Avalon-ST RX data interface or

XGMII. This feature is not available

when the Enable 10GBASE-R

register mode is enabled.

Altera recommends that you use the

same clock source for this clock and

rx_312_5_clk

. This clock must be

synchronous to

rx_312_5_clk

.

Their rising edges must align and

must have 0 ppm and phase-shift.

5-2

Clock and Reset Signals

UG-01144

2014.12.15

Altera Corporation

Interface Signals for LL Ethernet 10G MAC