Altera Low Latency Ethernet 10G MAC User Manual

Page 69

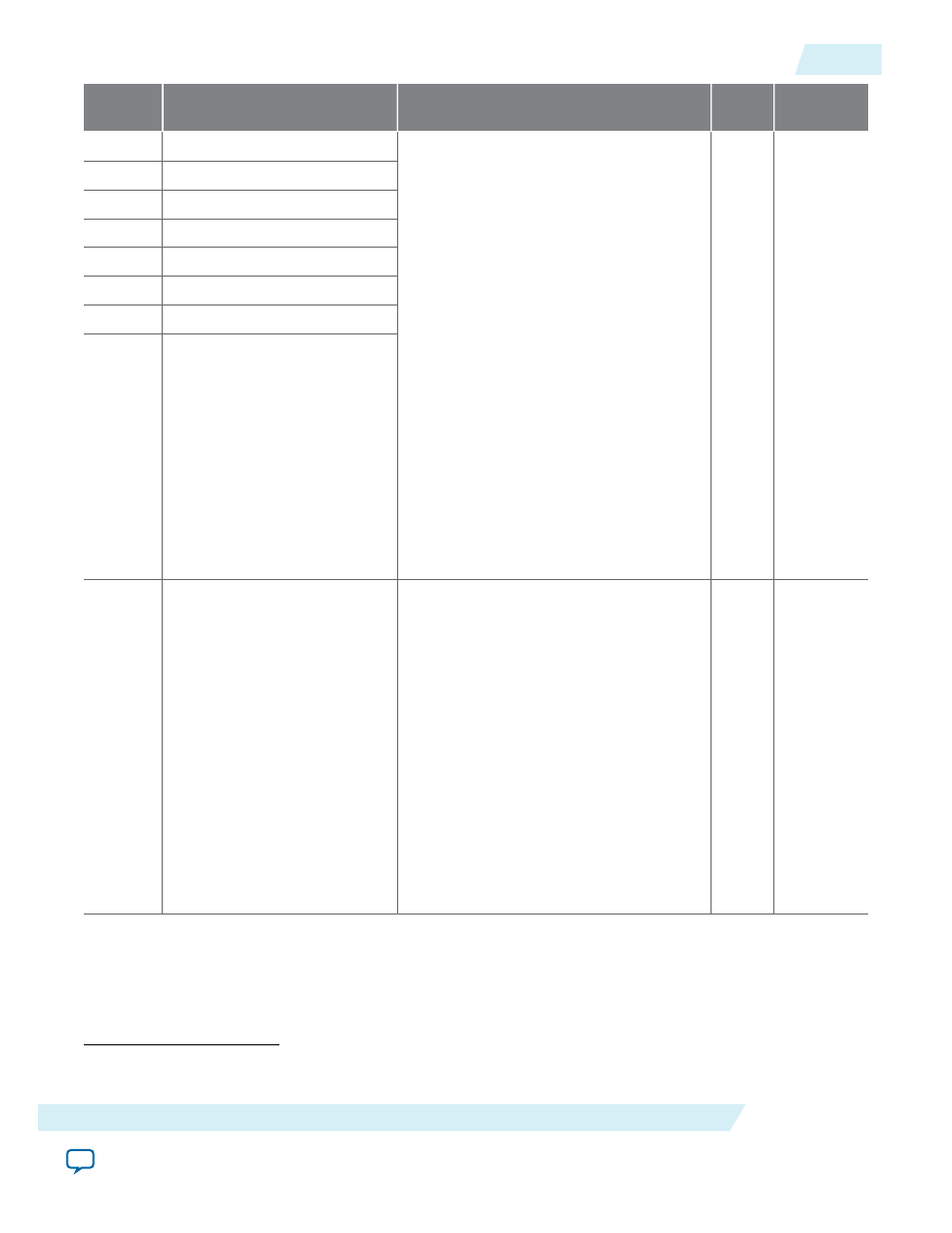

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x00B0

rx_frame_spaddr0_0

You can specify up to four 6-byte

supplementary addresses:

•

rx_framedecoder_spaddr0_0/1

•

rx_framedecoder_spaddr1_0/1

•

rx_framedecoder_spaddr2_0/1

•

rx_framedecoder_spaddr3_0/1

Configure the supplementary addresses

before you enable the MAC RX datapath.

Map the supplementary addresses to the

respective registers in the same manner as

the primary MAC address. Refer to the

description of

primary_mac_addr0

and

primary_mac__addr1

.The MAC IP core

uses the supplementary addresses to filter

unicast frames when the following

conditions are set:

• The use of the supplementary addresses

are enabled using the respective bits in

the

rx_frame_control

register.

• The

en_allucast

bit of the

rx_frame_

control

register is set to 0.

RW

0x0

0x00B1

rx_frame_spaddr0_1

0x00B2

rx_frame_spaddr1_0

0x00B3

rx_frame_spaddr1_1

0x00B4

rx_frame_spaddr2_0

0x00B5

rx_frame_spaddr2_1

0x00B6

rx_frame_spaddr3_0

0x00B7

rx_frame_spaddr3_1

0x00C0

rx_pfc_control

(8)

• Bits 7:0—enables priority-based flow

control on the RX datapath. Setting bit n

enables priority-based flow control for

priority queue n. For example, setting

rx_pfc_control[0]

enables queue 0.

• Bits 15:9—reserved.

• Bit 16—configures the forwarding of

priority-based control frames to the

client.

0: Drops the control frames.

1: Forwards the control frames to the

client.

• Bits 31:17—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x1

(8)

This register is used only when you turn on the Enable priority-based flow control (PFC) option. It is

reserved when not used.

UG-01144

2014.12.15

RX Configuration and Status Registers

4-17

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation