Rx configuration and status registers, Rx configuration and status registers -13 – Altera Low Latency Ethernet 10G MAC User Manual

Page 65

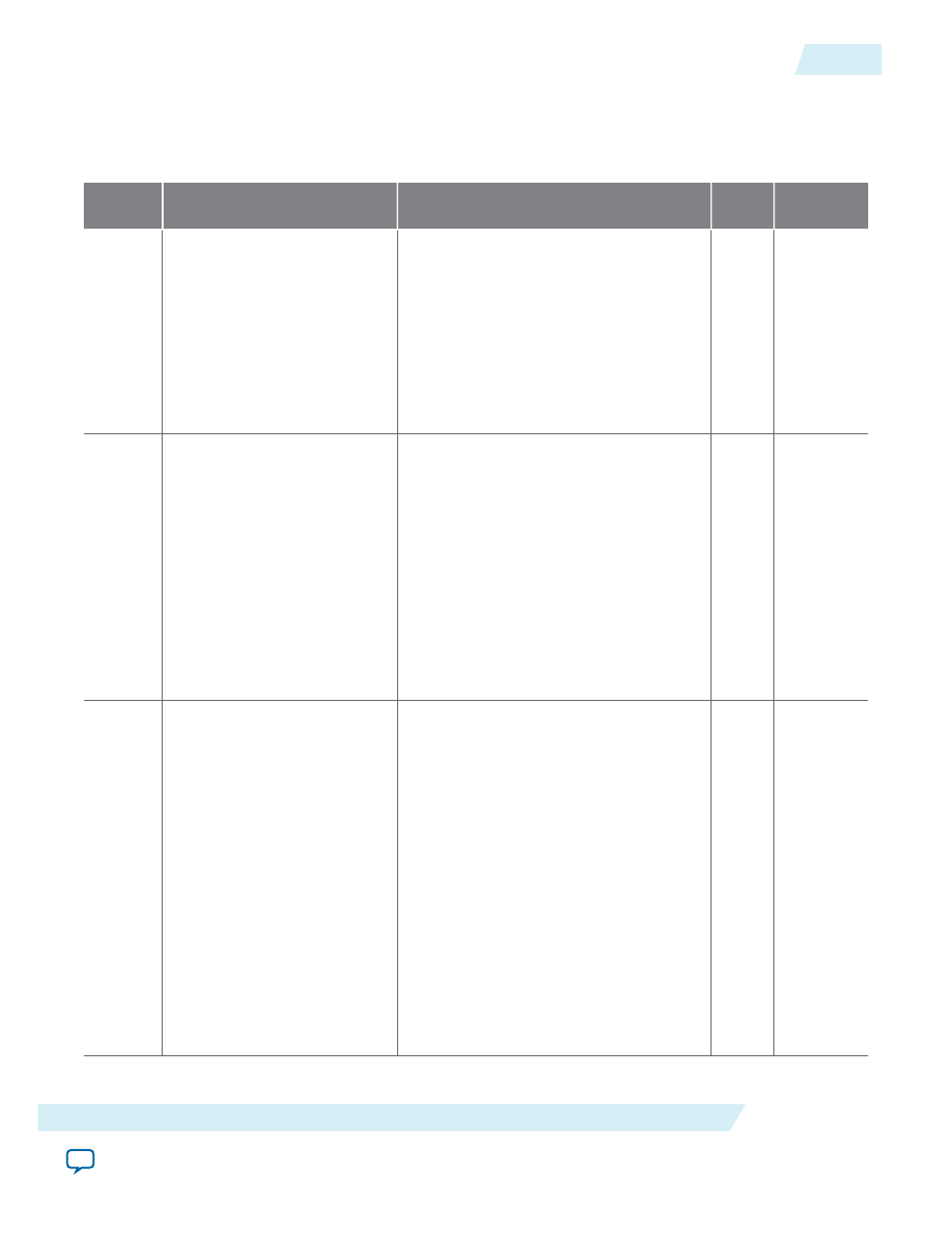

RX Configuration and Status Registers

Table 4-9: RX Configuration and Status Registers

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x00A0

rx_transfer_control

• Bit 0—RX path enable.

0: Enables the RX path.

1: Disables the RX path. The MAC IP

core drops all incoming frames.

• Bits 31:1—reserved.

A change of value in this register takes

effect at a packet boundary. Any transfer in

progress is not affected.

RW

0x0

0x00A2

rx_transfer_status

The MAC sets the following bits to indicate

the status of the RX datapath.

• Bits 7:0—reserved.

• Bit 8: RX datapath status.

0: The RX datapath is idle.

1: An RX data transfer is in progress.

• Bits 11:9—reserved.

• Bit 12: RX datapath reset status.

0: The RX datapath is not in reset.

1: The RX datapath is in reset.

RO

0x0

0x00A4

rx_padcrc_control

• Bits [1:0]—Padding and CRC removal

on receive.

00: Retains the padding bytes and CRC

field, and forwards them to the client.

01: Retains only the padding bytes. The

MAC IP core removes the CRC field

before it forwards the RX frame to the

client.

11: Removes the padding bytes and CRC

field before the RX frame is forwarded to

the client.

10: Reserved.

• Bits 31:2—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x1

UG-01144

2014.12.15

RX Configuration and Status Registers

4-13

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation