Calculating rx timing adjustments, Calculating rx timing adjustments -23 – Altera Low Latency Ethernet 10G MAC User Manual

Page 75

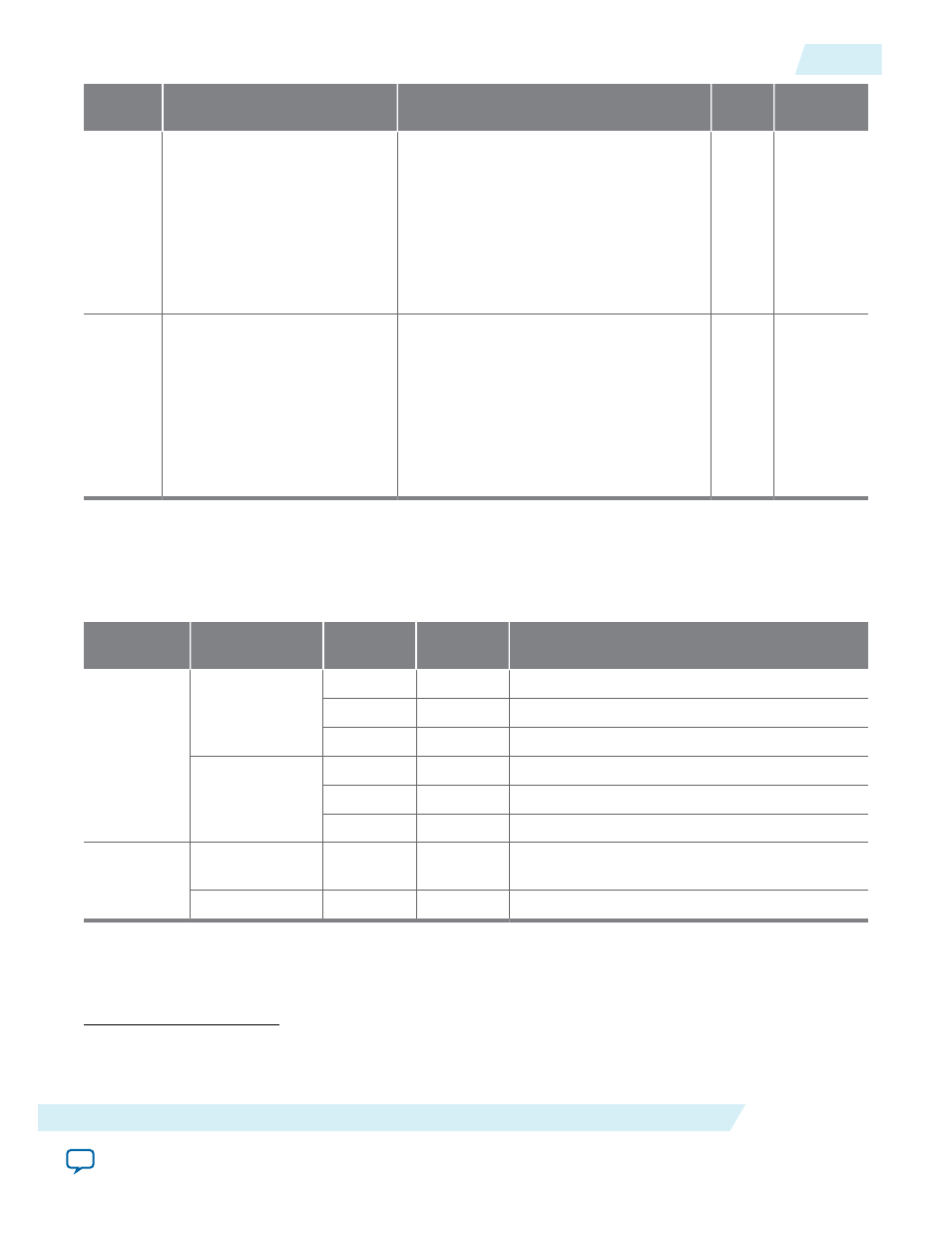

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x12A

rx_fns_adjustment_mult_

speed

Static timing adjustment in fractional

nanoseconds on the RX datapath for 10M/

100M/1G operations.

• Bits 15:0—adjustment period in

fractional nanoseconds.

• Bits 31:16—reserved. Set these bits to 0.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

0x12C

rx_ns_adjustment_mult_

speed

Static timing adjustment in nanoseconds on

the RX datapath for 10M/100M/1G

operations.

• Bits 15:0—adjustment period in

nanoseconds.

• Bits 31:16—reserved. Set these bits to 0.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

Calculating RX Timing Adjustments

You can derive the required timing adjustments in ns and fns from the hardware PMA delay.

Table 4-15: Hardware PMA Delay

Type

Device

PMA Mode

(bit)

Latency

(11)

MAC Configurations

Digital

Arria V GZ and

Stratix V

40

87 UI

10GbE or 10G of 10M-10GbE

32

84 UI

10GbE

10

26 UI

1G/100M/10M of 10M-10GbE

Arria 10

40

66.5 UI

10GbE or 10G of 10M-10GbE

32

58.5 UI

10GbE or 10G of 10M-10GbE

10

24.5 UI

1G/100M/10M of 10M-10GbE

Analog

(12)

Arria V GZ and

Stratix V

—

1.75 ns

All

Arria 10

—

1.75 ns

All

The example below shows the required calculation for a 10M – 10GbE design targeting a Stratix V device.

(11)

For 10G: 1 UI = 97 ps; for 10M/100M/1G: 1 UI = 800 ps

(12)

Valid for the HSSI clock routing using periphery clock. Other clocking scheme might result in deviation of a

few ns.

UG-01144

2014.12.15

Calculating RX Timing Adjustments

4-23

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation