Crc-32 insertion, Crc-32 insertion -5 – Altera Low Latency Ethernet 10G MAC User Manual

Page 27

CRC-32 Insertion

By default, the MAC TX computes and inserts CRC-32 checksum into TX frames. The MAC TX

computes the CRC-32 checksum over frame bytes that include the source address, destination address,

length, data, and padding bytes. The computation excludes the preamble and SFD bytes. The MAC TX

then inserts the CRC-32 checksum into the TX frame. Bit 31

st

of the checksum occupies the least signifi‐

cant bit of the first byte in the CRC field.

You can disable this function by setting the

tx_crc_control[1]

register bit to 0.

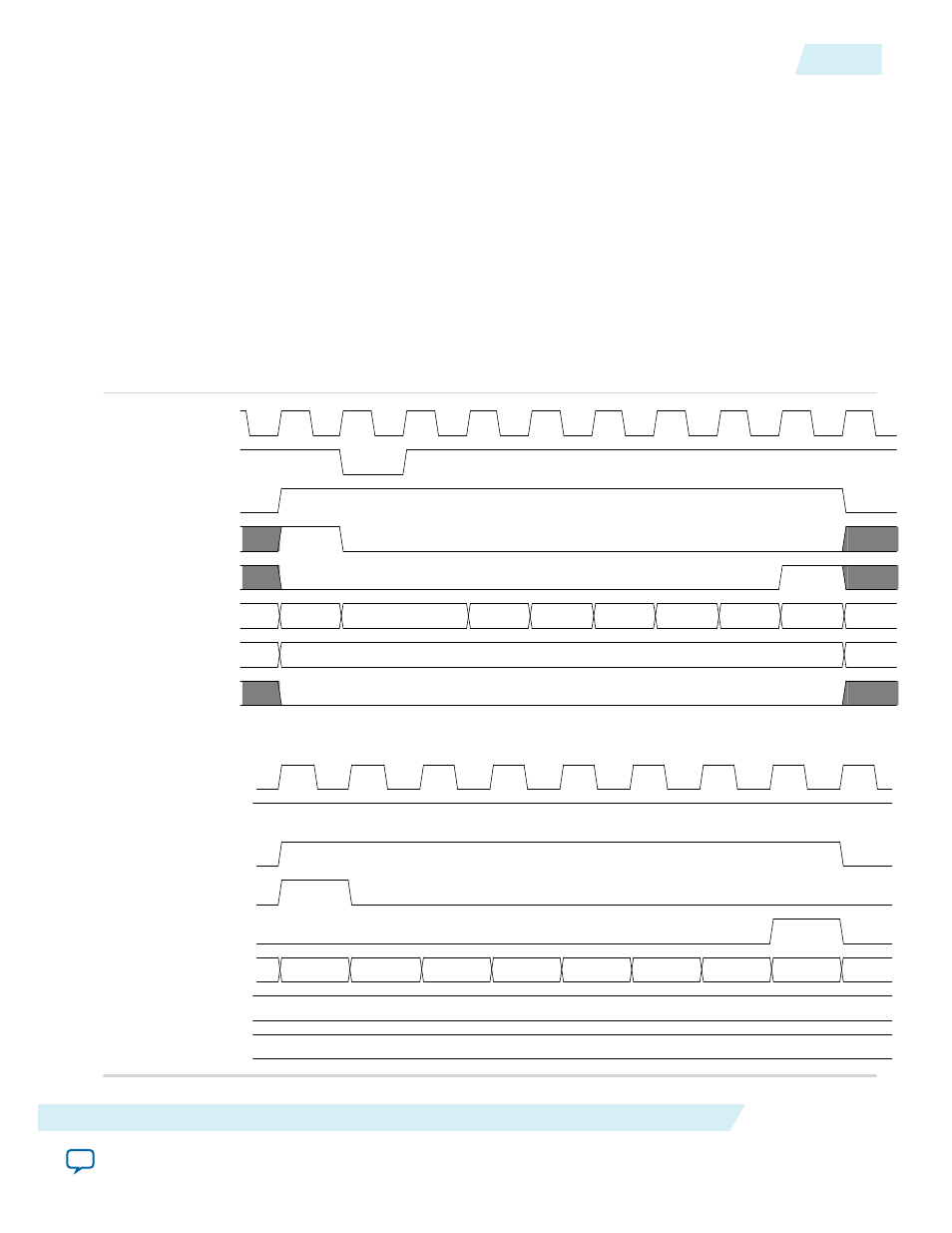

The following figure shows the timing diagram on the Avalon-ST data interfaces where CRC insertion is

enabled on transmit and CRC removal is disabled on receive. The frame from the client is without

CRC-32 checksum. The MAC TX inserts the CRC-32 checksum (4EB00AF4) into the frame. The frame is

then looped back to the RX datapath with the CRC-32 checksum.

Figure 3-4: Avalon-ST TX and RX Interfaces with CRC Insertion Enabled

tx_312_5_clk

avalon_st_tx_ready

avalon_st_tx_valid

avalon_st_tx_startofpacket

avalon_st_tx_endofpacket

avalon_st_tx_data[31:0]

avalon_st_tx_empty[1:0]

avalon_st_tx_error

...00000000

0

rx_312_5_clk

avalon_st_rx_ready

avalon_st_rx_valid

avalon_st_rx_startofpacket

avalon_st_rx_endofpacket

avalon_st_rx_data[31:0]

avalon_st_rx_empty[1:0]

avalon_st_rx_error[5:0]

...4EB30AF4

0

UG-01144

2014.12.15

CRC-32 Insertion

3-5

Functional Description of LL Ethernet 10G MAC

Altera Corporation