Xgmii rx signals, Xgmii rx signals -15 – Altera Low Latency Ethernet 10G MAC User Manual

Page 97

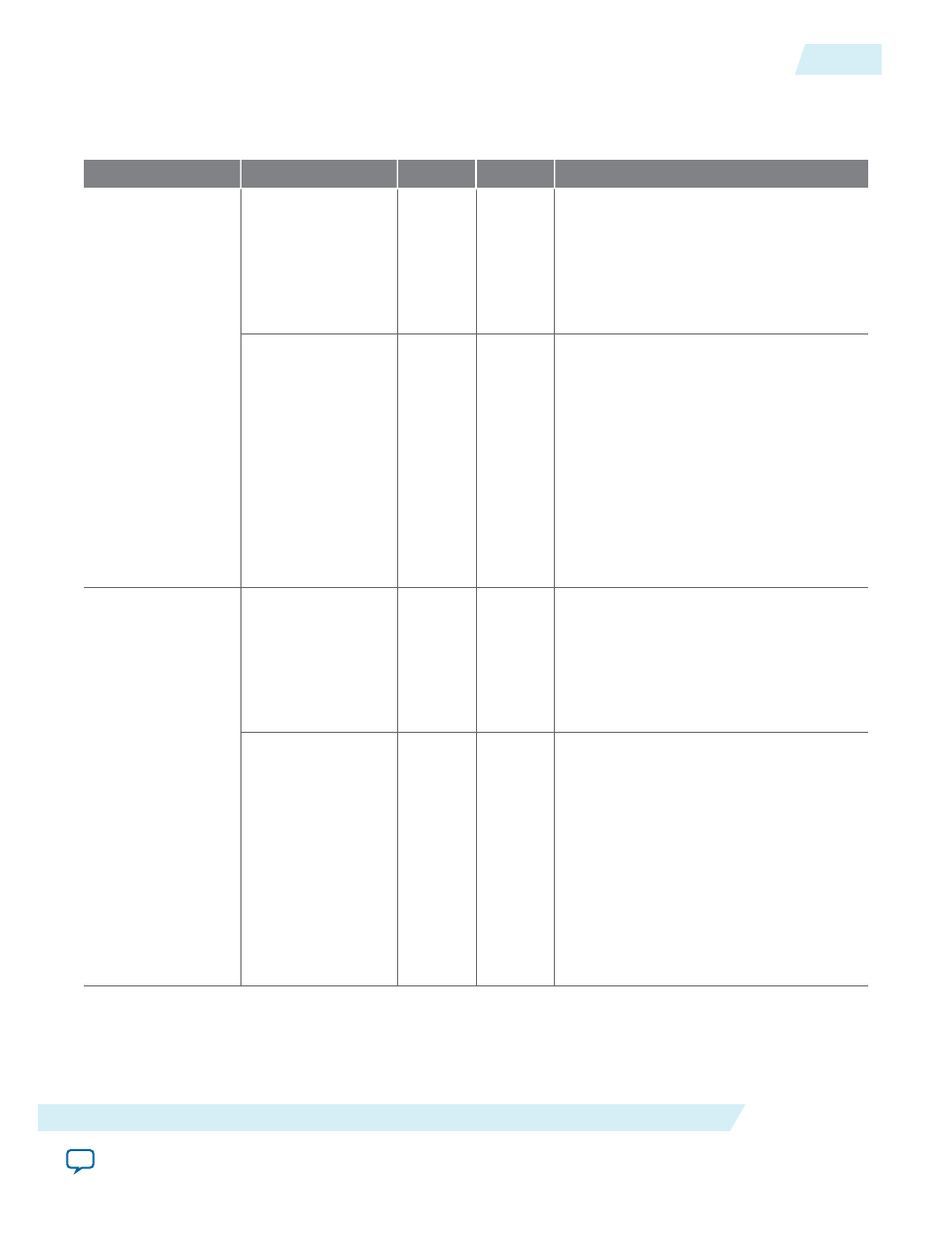

XGMII RX Signals

Table 5-12: XGMII Receive Signals

Signal

Condition

Direction

Width

Description

xgmii_rx_

data[]

Use legacy Ethernet

10G MAC XGMII

interface disabled.

Enable 10GBASE-R

register mode

disabled.

In

32

4-lane RX data bus. Lane 0 starts from

the least significant bit.

• Lane 0:

xgmii_rx_data[7:0]

• Lane 1:

xgmii_rx_data[15:8]

• Lane 2:

xgmii_rx_data[23:16]

• Lane 3:

xgmii_rx_data[31:24]

Use legacy Ethernet

10G MAC XGMII

interface disabled.

Enable 10GBASE-R

register mode

enabled.

In

64

8-lane SDR XGMII receive data. This

signal connects directly to the Native

PHY IP core.

• Lane 0:

xgmii_rx_data[7:0]

• Lane 1:

xgmii_rx_data[15:8]

• Lane 2:

xgmii_rx_data[23:16]

• Lane 3:

xgmii_rx_data[31:24]

• Lane 4:

xgmii_rx_data[39:32]

• Lane 5:

xgmii_rx_data[47:40]

• Lane 6:

xgmii_rx_data[55:48]

• Lane 7:

xgmii_rx_data[63:56]

xgmii_rx_

control[]

Use legacy Ethernet

10G MAC XGMII

interface disabled.

Enable 10GBASE-R

register mode

disabled.

In

4

Control bits for each lane in

xgmii_rx_

data[]

.

• Lane 0:

xgmii_rx_control[0]

• Lane 1:

xgmii_rx_control[1]

• Lane 2:

xgmii_rx_control[2]

• Lane 3:

xgmii_rx_control[3]

Use legacy Ethernet

10G MAC XGMII

interface disabled.

Enable 10GBASE-R

register mode

enabled.

In

8

8-lane SDR XGMII receive control. This

signal connects directly to the

NativePHY IP core.

• Lane 0:

xgmii_rx_control[0]

• Lane 1:

xgmii_rx_control[1]

• Lane 2:

xgmii_rx_control[2]

• Lane 3:

xgmii_rx_control[3]

• Lane 4:

xgmii_rx_control[4]

• Lane 5:

xgmii_rx_control[5]

• Lane 6:

xgmii_rx_control[6]

• Lane 7:

xgmii_rx_control[7]

UG-01144

2014.12.15

XGMII RX Signals

5-15

Interface Signals for LL Ethernet 10G MAC

Altera Corporation