Altera Low Latency Ethernet 10G MAC User Manual

Page 46

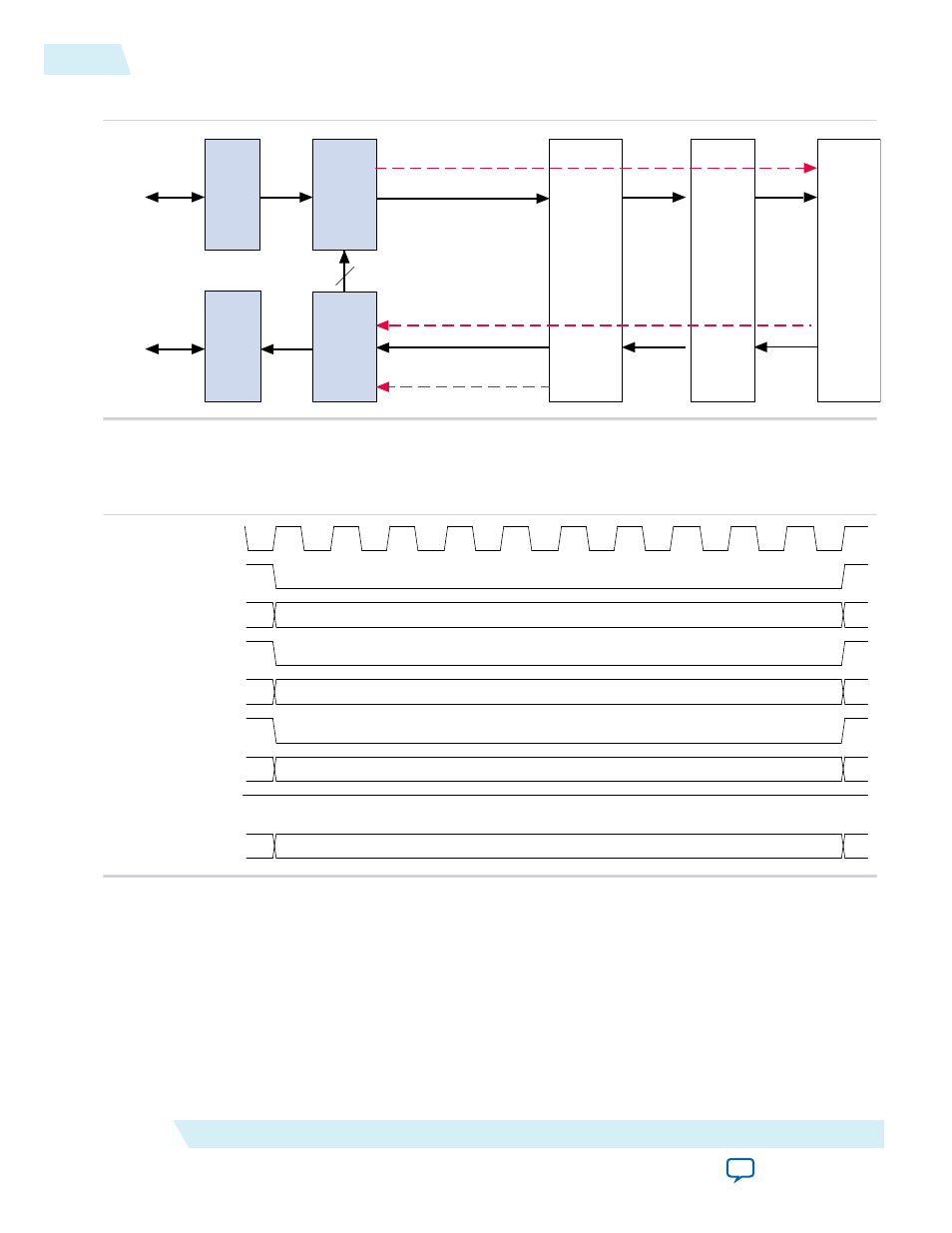

Figure 3-20: Fault Signaling

Remote Fault (0x9c000002)

Idle (07070707)

Remote Fault (0x9c000002)

Client

Interface

MAC

Tx

RS Tx

MAC

Rx

RS Rx

2

link_fault_status_xgmii_rx_data

XAUI /

10GBASE-R

PHY

External

PHY

Remote

Partner

XAUI /

10GBASE-R

Network

Interface

Local Fault (0x9c000001)

XGMII

Figure 3-21: XGMII TX interface Transmitting Remote Fault Signal

The following figure shows the timing for the XGMII TX interface transmitting the remote fault signal

(0x9c000002).

tx_clk_clk

xgmii_tx_control[3]

xgmii_tx_data[31:24]

xgmii_tx_control[2]

xgmii_tx_data[23:16]

xgmii_tx_control[1]

xgmii_tx_data[15:8]

xgmii_tx_control[0]

xgmii_tx_data[7:0]

02

00

00

9C

When you instantiate the MAC RX only variation, connect the

link_fault_status_xgmii_rx_data

signal to the corresponding RX client logic to handle the link fault. Similarly, when you instantiate the

MAC TX only variation, connect the

link_fault_status_xgmii_tx_data

signal to the corresponding

TX client logic.

3-24

XGMII Error Handling (Link Fault)

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC