Avalon-st rx data interface signals, Avalon-st rx data interface signals -6 – Altera Low Latency Ethernet 10G MAC User Manual

Page 88

Signal

Direction

Width

Description

avalon_st_tx_

empty[]

In

2

Use this signal to specify the number of empty bytes

(not used) in the cycle that contain the end of a

packet.

• 0x0: All bytes are valid.

• 0x1: The last byte is invalid.

• 0x2: The last two bytes are invalid.

• 0x3: The last three bytes are invalid.

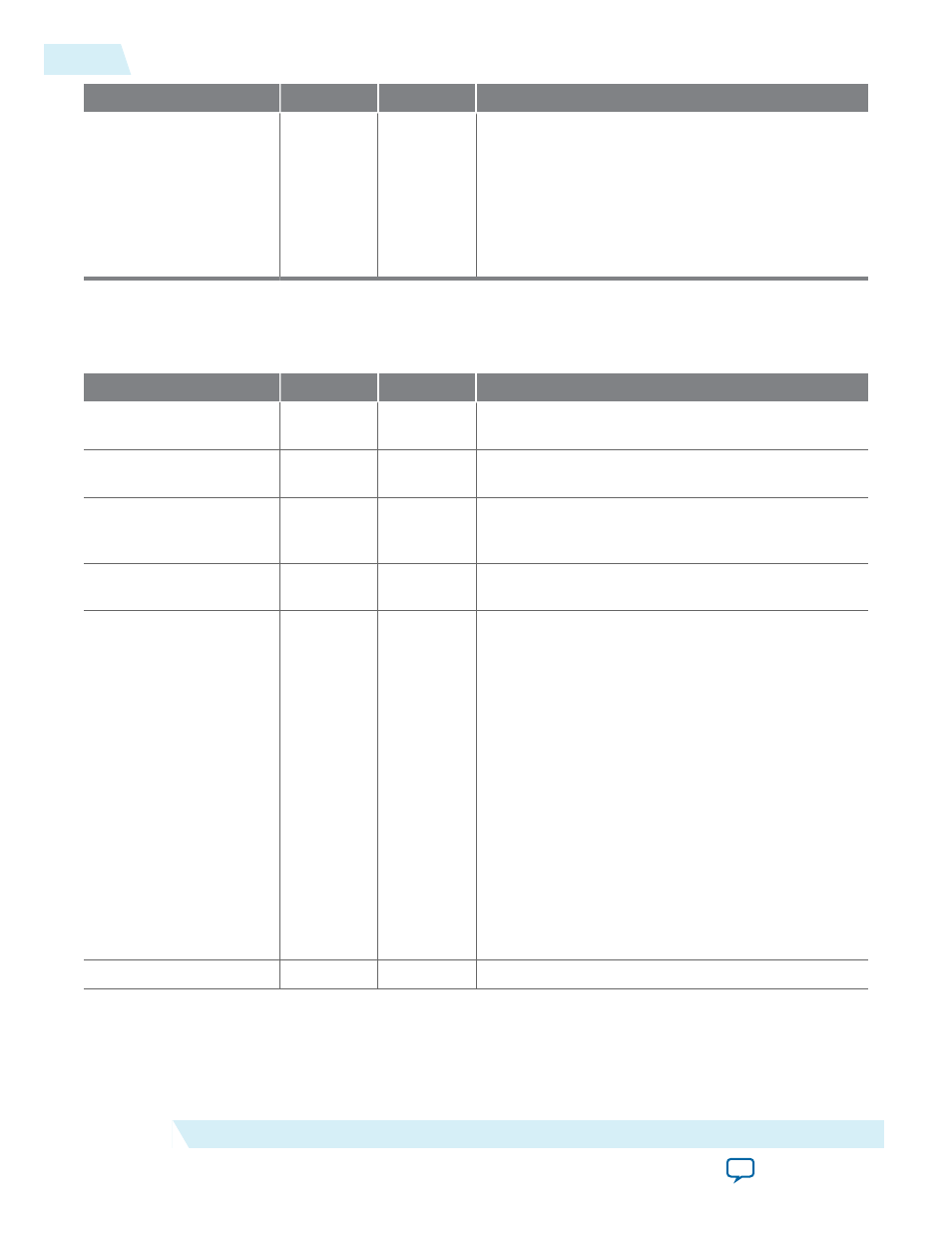

Avalon-ST RX Data Interface Signals

Table 5-7: Avalon-ST RX Data Interface Signals

Signal

Direction

Width

Description

avalon_st_rx_

startofpacket

Out

1

When asserted, indicates the beginning of the RX

data.

avalon_st_rx_

endofpacket

Out

1

When asserted, indicates the end of the RX data.

avalon_st_rx_valid

Out

1

When asserted, indicates that the

avalon_st_rx_

data[]

signal and other signals on this interface are

valid.

avalon_st_rx_ready

In

1

Assert this signal when the client is ready to accept

data.

avalon_st_rx_

error[]

Out

6

When set to 1, the respective bits indicate an error

type:

• Bit 0—PHY error.

• For 10 Gbps, the data on

xgmii_rx_data

contains a control error character (FE).

• For 10 Mbps,100 Mbps,1 Gbps,

gmii_rx_err

or

mii_rx_err

is asserted.

• Bit 1—CRC error. The computed CRC value

does not match the CRC received.

• Bit 2—Undersized frame. The RX frame length

is less than 64 bytes.

• Bit 3—Oversized frame.

• Bit 4—Payload length error.

• Bit 5—Overflow error. The user application is

not ready to receive more data while still

receiving incoming data from the MAC IP core.

avalon_st_rx_data[]

Out

32

RX data to the client.

5-6

Avalon-ST RX Data Interface Signals

UG-01144

2014.12.15

Altera Corporation

Interface Signals for LL Ethernet 10G MAC