Altera Low Latency Ethernet 10G MAC User Manual

Page 74

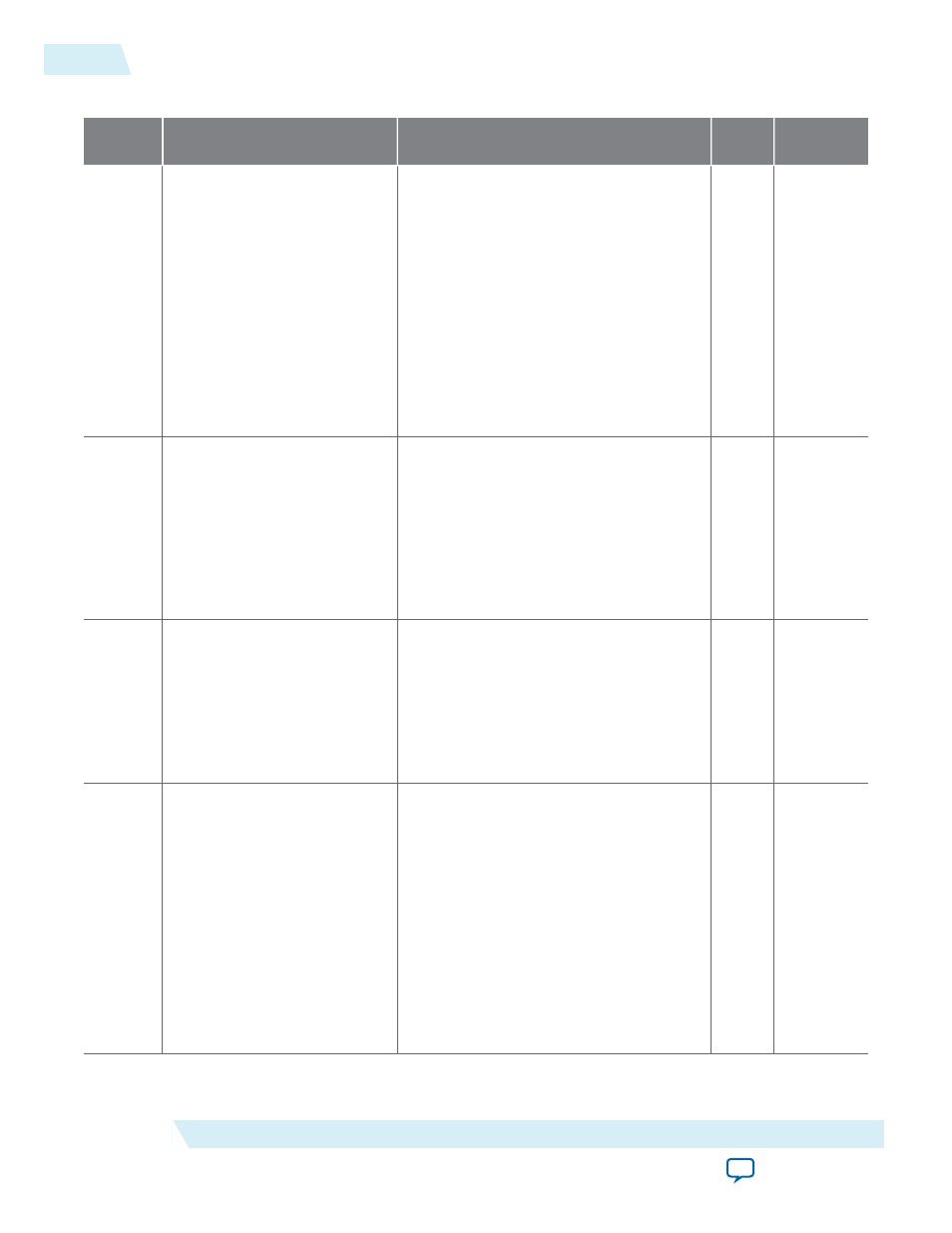

Table 4-14: RX Timestamp Registers

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0120

rx_period_10G

Specifies the clock period on the RX

datapath for 10G operations. The MAC IP

core multiplies the value of this register by

the number of stages separating the actual

timestamp and XGMII bus.

• Bits 15:0—period in fractional nanosec‐

onds.

• Bits 19:16—period in nanoseconds.

• Bits 31:20—reserved.

The default value is 3.2 ns for 312.5 MHz

clock. Configure this register before you

enable the MAC IP core for operations.

RW

0x33333

0x0122

rx_fns_adjustment_10G

Static timing adjustment in fractional

nanoseconds on the RX datapath for 10G

operations.

• Bits 15:0—adjustment period in

fractional nanoseconds.

• Bits 31:16—reserved. Set these bits to 0.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

0x0124

rx_ns_adjustment_10G

Static timing adjustment in nanoseconds on

the RX datapath for 10G operations.

• Bits 15:0—adjustment period in

nanoseconds.

• Bits 31:16—reserved. Set these bits to 0.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

0x0128

rx_period_mult_speed

Specifies the clock period on the RX

datapath for 10M/100M/1G operations. The

MAC IP core multiplies the value of this

register by the number of stages separating

the actual timestamp and GMII/MII bus.

• Bits 15:0—period in fractional nanosec‐

onds.

• Bits 19:16—period in nanoseconds.

• Bits 31:20—reserved. Set these bits to 0.

The default value is 8 ns for 125 MHz clock.

Configure this register before you enable

the MAC IP core for operations.

RW

0x80000

4-22

RX Timestamp Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC