Altera Low Latency Ethernet 10G MAC User Manual

Page 108

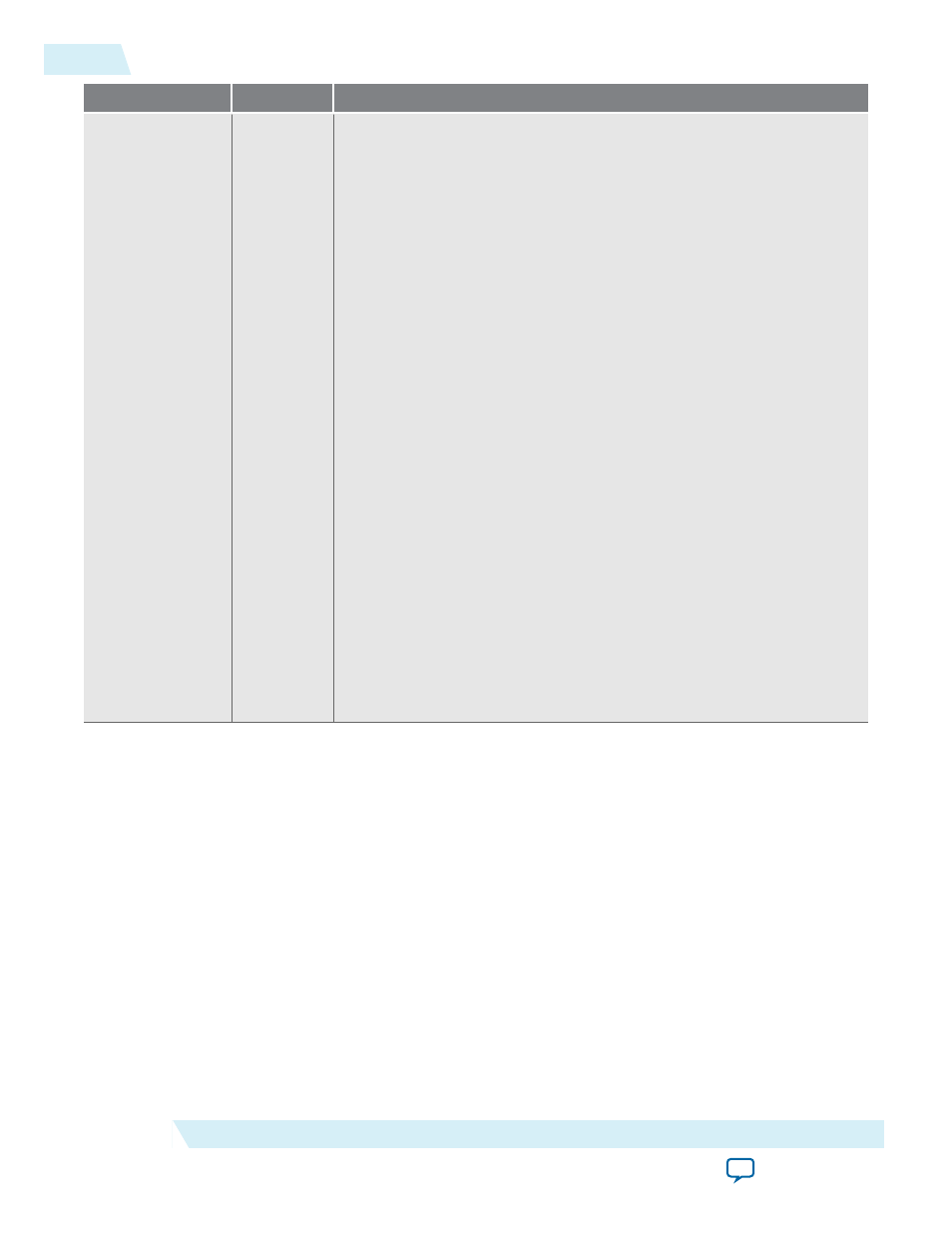

Date

Version

Changes

December 2014

2014.12.15 • Updated the Performance and Resource Utilization table—improved

the resource utilization for IEEE 1588v2 feature.

• Added a new feature—10GBASE-R register mode:

• Added a new parameter—Enable 10GBASE-R register mode.

• Added new signals—

tx_xcvr_clk

,

rx_xcvr_clk

,

xgmii_tx_

valid

,

xgmii_rx_valid

.

• Added new parameter options for Time of Day Format.

• Added a new table in the Frame Type Checking topic to describe the

MAC behavior for different frame types.

• Added a new table—Register Access Type Convention—to describe

the access type for the IP core registers.

• Added a new section about timing constraints.

• Revised the receive timestamp registers word offset to start from

0x0120 to 0x012C.

• Added a recommendation for the

csr_rst_n

signal—deassert the

csr_rst_n

signal at least once after

tx_clk

and

rx_clk

are stable.

• Revised the number of bits for fractional number of clock cycle for

rx_path_delay_10g_data

and

rx_path_delay_1g_data

signals to

Bit [9:0]: Fractional number of clock cycle, Bit [21/15:10]:Number of

clock cycle.

• Updated the signals description for:

•

tx_egress_timestamp_request_fingerprint[]

•

tx_egress_timestamp_96b_data[]

•

tx_egress_timestamp_64b_data[]

•

tx_time_of_day_96b_1g_data

•

tx_time_of_day_64b_1g_data

A-2

Low Latency Ethernet 10G MAC User Guide Document Revision History

UG-01144

2014.12.15

Altera Corporation

Additional Information