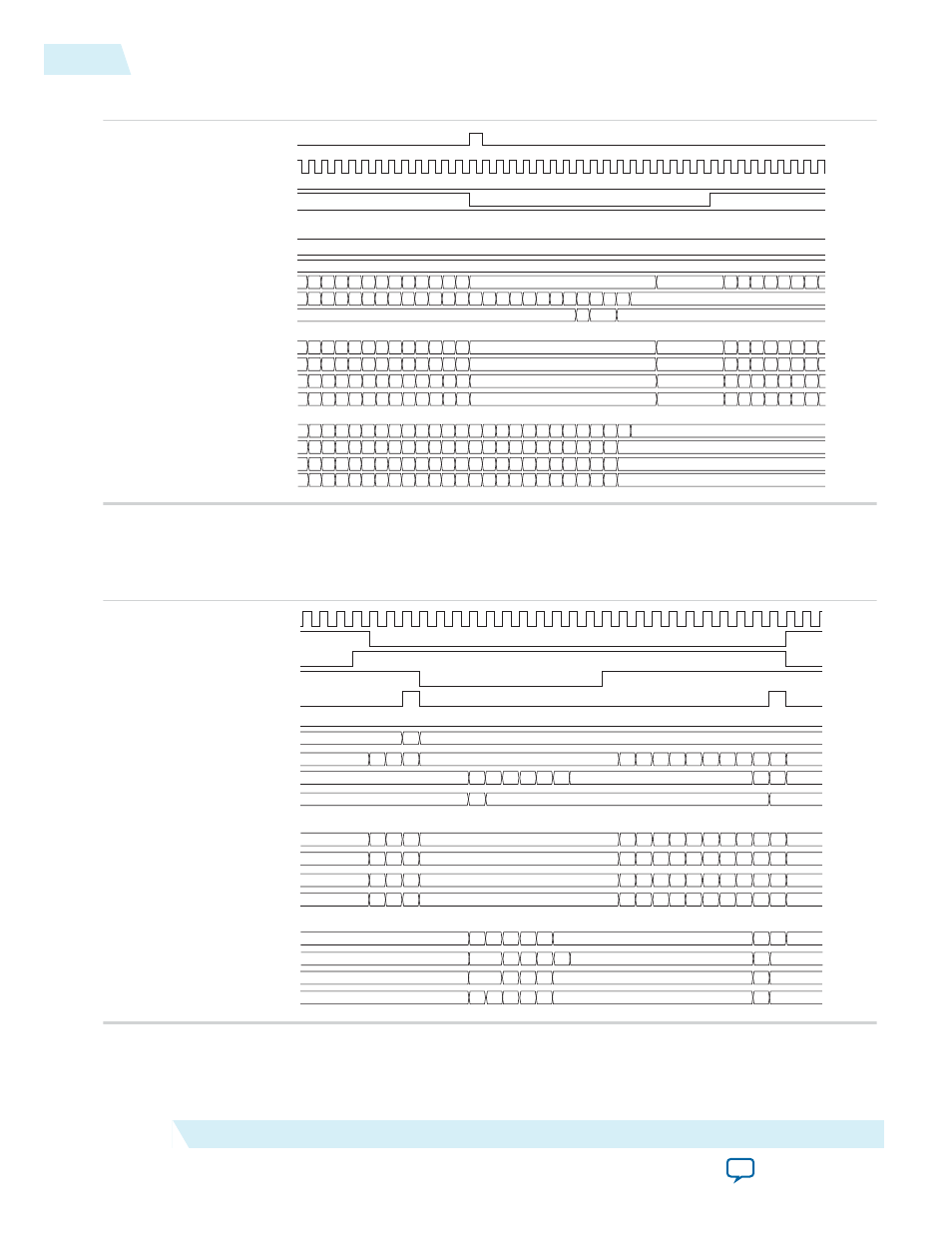

Figure 3-12: error condition—underflow, continued – Altera Low Latency Ethernet 10G MAC User Manual

Page 34

Figure 3-12: Error Condition—Underflow, continued

tx_312_5_clk

avalon_st_tx_startofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_endofpacket

avalon_st_tx_error

avalon_st_tx_empty[1:0]

avalon_st_tx_data[31:0]

xgmii_tx_data[31:0]

xgmii_tx_control[3:0]

avalon_st_tx_data[31:24]

avalon_st_tx_data[23:16]

avalon_st_tx_data[15:8]

avalon_st_tx_data[7:0]

xgmii_tx_data[7:0]

xgmii_tx_data[15:8]

xgmii_tx_data[23:16]

xgmii_tx_data[31:24]

pulse_tx_udf_errcnt

* *4 *f *3 *c *1 *e *d *a *c *e *9 *7

c531_fcb6

*c *d *9 *e *3 *e *4 *5 *d *2 *c *f *f *6 *0 *3 *6 *fe *7

0707_0707

0

f

0

f

fe

d9 6e 63 6e 74 d5 ed 42 cc 3f 5f 76 c0 93 b6

07

fe

1e c7 2f 1b 0c 02 37 39 3b

31

07

fe

95 46 23 39 c1 d4 fc a9 4a 37 8b 13 f0

07

fe

48 c8 3f 14 84 6f 23 33 a1 5e 8d 1a fc 1e 49

07

fd

37 b8

a4 3a

37 e3

37 13

15

* *1 *6 *1

*8 *d

*8 *6 *5 *2 *5

b793_b875

*b *7 *

6e 74 d5 ed 42 cc 3f 5d 76 c0 93 b6 37

c5

de ad bd b0 71

b7

d6 23 5

c7 2f 1b 0c 02 37 39 3b 15 31 cd 99 a4

31

79 37 c6 0d 36

93

d5 d4 a

46 23 39 c1 d4 fc a9 4a 37 8b 13 f0 37

fc

ec e2 1e 6b ca

b8

95 d8 8

14 84 6f 23 33 a1 5e 8d 1a fc 1e 49 37

b6

48 16 a5 52 d5

75

2b d7 0

c1

7a

6d

61

cd 99

ff d1 e6 c1 3c ad

c1 01 51 35

41 c3 42 3a

95 44 a2 61 16 05

f7

20

72

5d

Figure 3-13: Short Frame with Padding Bytes Insertion Enabled

The following diagram shows the transmission of a short frame with no payload data. Padding bytes

insertion is enabled.

tx_312_5_clk

avalon_st_tx_startofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_endofpacket

avalon_st_tx_error

avalon_st_tx_empty[1:0]

avalon_st_tx_data[31:0]

xgmii_tx_data[31:0]

xgmii_tx_control[3:0]

avalon_st_tx_data[31:24]

avalon_st_tx_data[23:16]

avalon_st_tx_data[15:8]

avalon_st_tx_data[7:0]

xgmii_tx_data[7:0]

xgmii_tx_data[15:8]

xgmii_tx_data[23:16]

xgmii_tx_data[31:24]

0

2

*c

0

92e6_9b29

*f *2

1626_4dfe

*e *6 *5 *a *e *1 *e *f *a *b

*b

0707_0707

*5 *1

0000_0000

*e *6

*0 *2 *0

f

1

0

c0

81

4f 00

16

2f 57 ee fe 13 f0 2d d2 5c 9d

d0

90

e0 2e

26

a8 57 cf c3 d3 e9 87 52 ca 63

ae

a0

66 a0

4d

d8 ea 91 b8 b5 b0 9f ad e0 d7

ac

b0

8f f2

fe

de e6 85 3a 8e 61 be af 0a 4b

fb

07

55 81

00

9f fd

c0 22

07

55

90

00

de

d0 33 2e

07

55

a0

00

6c

00 44

07

b0

00

15

00 55

55 d5

3-12

TX Timing Diagrams

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC