Altera Low Latency Ethernet 10G MAC User Manual

Page 67

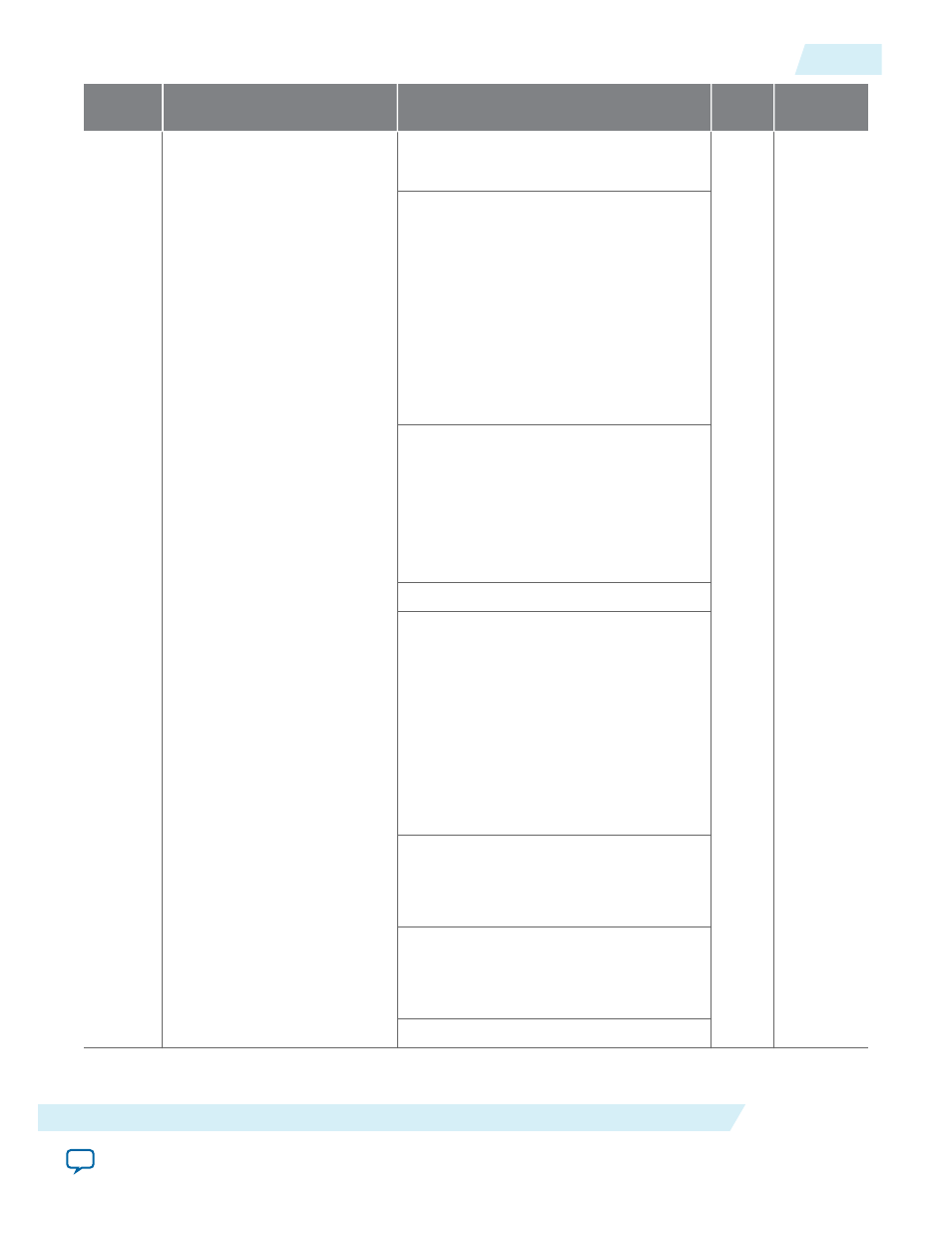

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x00AC

rx_frame_control

Configure this register before you enable

the MAC IP core for operations.

RW

0x3

Bit 0—

EN_ALLUCAST

0: Filters RX unicast frames using the

primary MAC address. The MAC IP core

drops unicast frames with a destination

address other than the primary MAC

address.

1: Accepts all RX unicast frames.

Setting this bit and the

EN_ALLMCAST

to 1

puts the MAC IP core in the promiscuous

mode.

Bit 1—

EN_ALLMCAST

0: Drops all RX multicast frames.

1: Accepts all RX multicast frames.

Setting this bit and the

EN_ALLUCAST

bit to 1

is equivalent to setting the MAC IP core to

the promiscuous mode.

Bit 2—reserved.

Bit 3—

FWD_CONTROL

. When you turn on the

Priority-based Flow Control parameter,

this bit affects all control frames except the

IEEE 802.3 pause frames and priority-based

control frames. When the Priority-based

Flow Control parameter is not enabled, this

bit affects all control frames except the IEEE

802.3 pause frames.

0: Drops the control frames.

1: Forwards the control frames to the client.

Bit 4—

FWD_PAUSE

0: Drops pause frames.

1: Forwards pause frames to the client.

Bit 5—

IGNORE_PAUSE

0: Processes pause frames.

1: Ignores pause frames.

Bits 15:6—reserved.

UG-01144

2014.12.15

RX Configuration and Status Registers

4-15

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation