Altera Low Latency Ethernet 10G MAC User Manual

Page 106

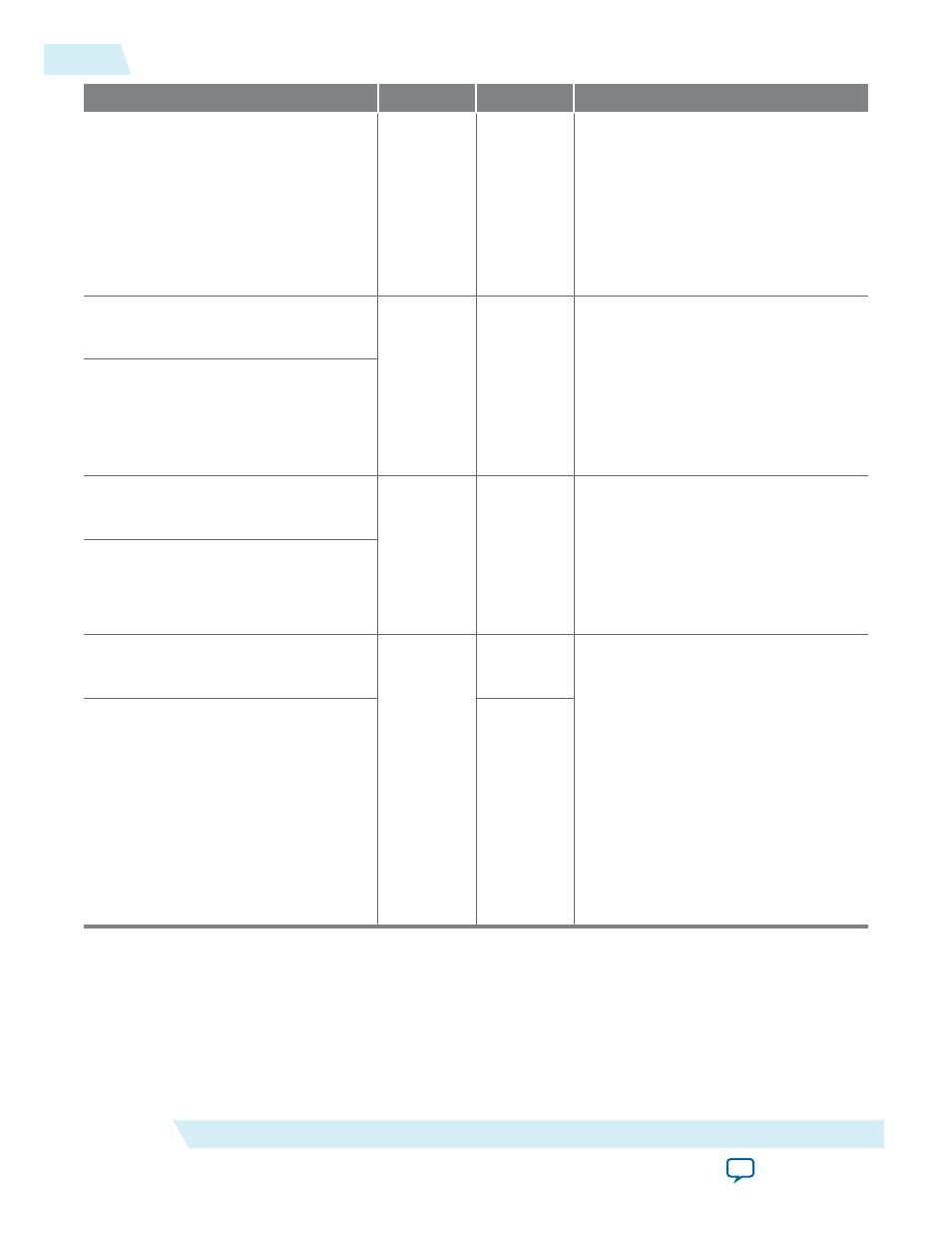

Signal

Direction

Width

Description

rx_ingress_timestamp_64b_data[]

Out

64

Carries the 64-bit ingress timestamp

in the following format:

• Bits 16 to 63: 48-bit nanoseconds

field

• Bits 0 to 15: 16-bit fractional

nanoseconds field

This timestamp is used in transparent

clock devices.

rx_time_of_day_96b_10g_data

(for 10 Gbps)

In

96

Carries the time of day (ToD) from

an external ToD module to the MAC

IP core in the following format:

• Bits 48 to 95: 48-bit seconds field

• Bits 16 to 47: 32-bit nanoseconds

field

• Bits 0 to 15: 16-bit fractional

nanoseconds field

rx_time_of_day_96b_1g_data

(for 10 Mbps and 100 Mbps)

rx_time_of_day_64b_10g_data

(for 10 Gbps)

In

64

Carries the ToD from an external

ToD module the MAC IP core in the

following format:

• Bits 16 to 63: 48-bit nanoseconds

field

• Bits 0 to 15: 16-bit fractional

nanoseconds field

rx_time_of_day_64b_1g_data

(for 10 Mbps and 100 Mbps)

rx_path_delay_10g_data

(for 10 Gbps)

In

16

Connect this bus to the Altera PHY

IP. This bus carries the path delay

(residence time), measured between

the physical network and the PHY

side of the MAC IP Core (XGMII,

GMII, or MII). The MAC IP core

uses this value when generating the

ingress timestamp to account for the

delay. The path delay is in the

following format:

• Bits 0 to 9: Fractional number of

clock cycle

• Bits 10 to 15/21: Number of clock

cycle

rx_path_delay_1g_data

(for 10 Mbps and 100 Mbps)

22

5-24

IEEE 1588v2 Ingress Receive Signals

UG-01144

2014.12.15

Altera Corporation

Interface Signals for LL Ethernet 10G MAC