Altera Low Latency Ethernet 10G MAC User Manual

Page 103

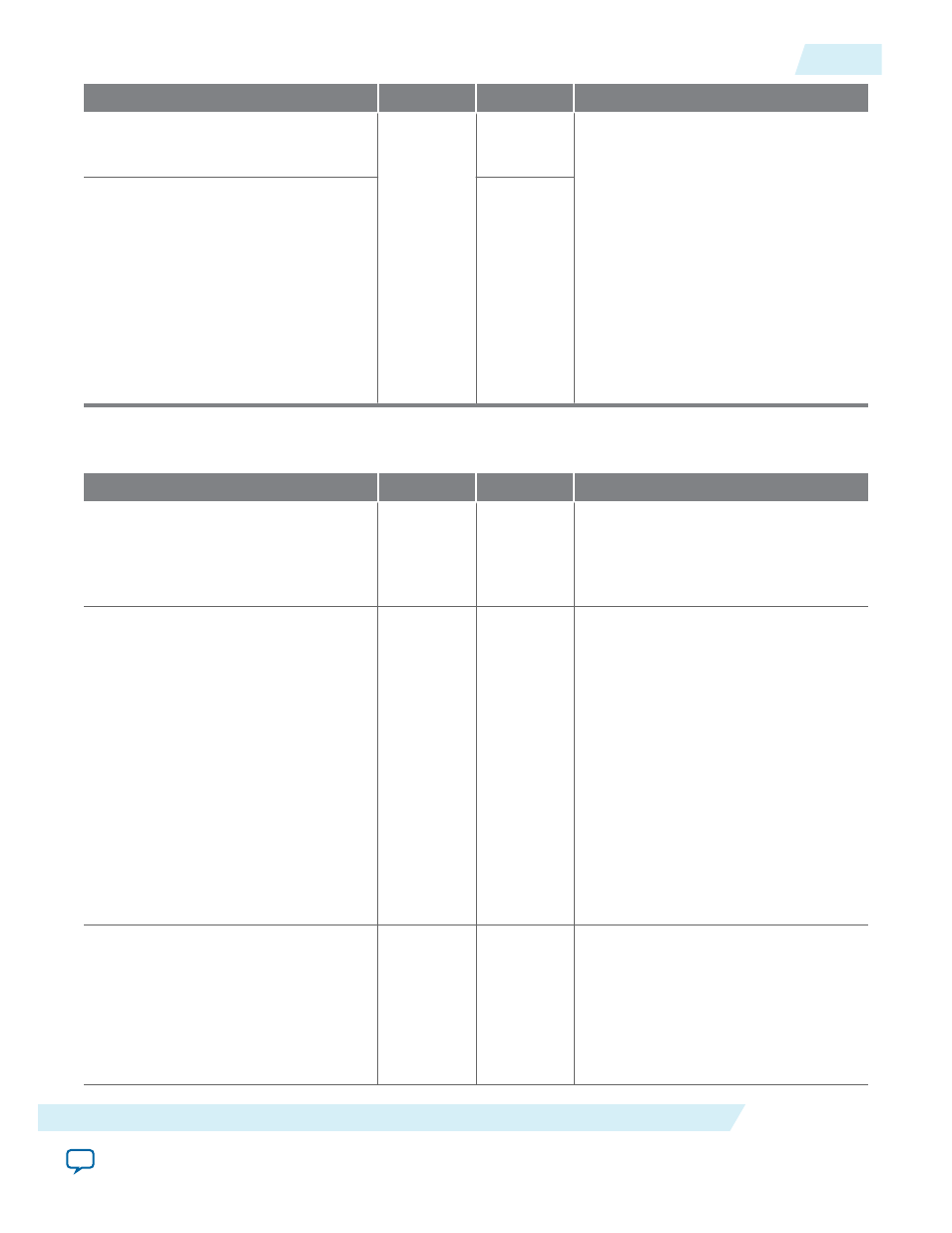

Signal

Direction

Width

Description

tx_path_delay_10g_data

(for 10 Gbps)

In

16

Connect this bus to the Altera PHY

IP. This bus carries the path delay,

which is measured between the

physical network and the PHY side of

the MAC IP Core (XGMII, GMII, or

MII). The MAC IP core uses this

value when generating the egress

timestamp to account for the delay.

The path delay is in the following

format:

• Bits 0 to 9: Fractional number of

clock cycle

• Bits 10 to 15/21: Number of clock

cycle

tx_path_delay_1g_data

(for 10 Mbps, 100 Mbps, and 1 Gbps)

22

Table 5-18: IEEE 1588v2 Egress Transmit Signals—1-step Mode

These signals apply to 1-step operation mode only.

Signal

Direction

Width

Description

tx_etstamp_ins_ctrl_timestamp_

insert

In

1

Assert this signal to insert egress

timestamp into the associated frame.

Assert this signal in the same clock

cycle avalon_st_tx_startofpacket is

asserted.

tx_etstamp_ins_ctrl_timestamp_

format

In

1

Use this signal to specify the format

of the timestamp to be inserted.

• 0: 1588v2 format (48-bits second

field + 32-bits nanosecond field +

16-bits correction field for

fractional nanosecond). Required

offset location of timestamp

andcorrection field.

• 1: 1588v1 format (32-bits second

field + 32-bits nanosecond field).

Required offset location of

timestamp.

Assert this signal in the same clock

cycle as the start of packet (avalon_

st_tx_startofpacket is asserted).

tx_etstamp_ins_ctrl_residence_

time_update

In

1

Assert this signal to add residence

time (egress timestamp –ingress

timestamp) into correction field of

PTP frame. Required offset location

of correction field. Assert this signal

in the same clock cycle as the start of

packet (avalon_st_tx_startofpacket is

asserted).

UG-01144

2014.12.15

IEEE 1588v2 Egress Transmit Signals

5-21

Interface Signals for LL Ethernet 10G MAC

Altera Corporation