Flow control registers, Flow control registers -10 – Altera Low Latency Ethernet 10G MAC User Manual

Page 62

Flow Control Registers

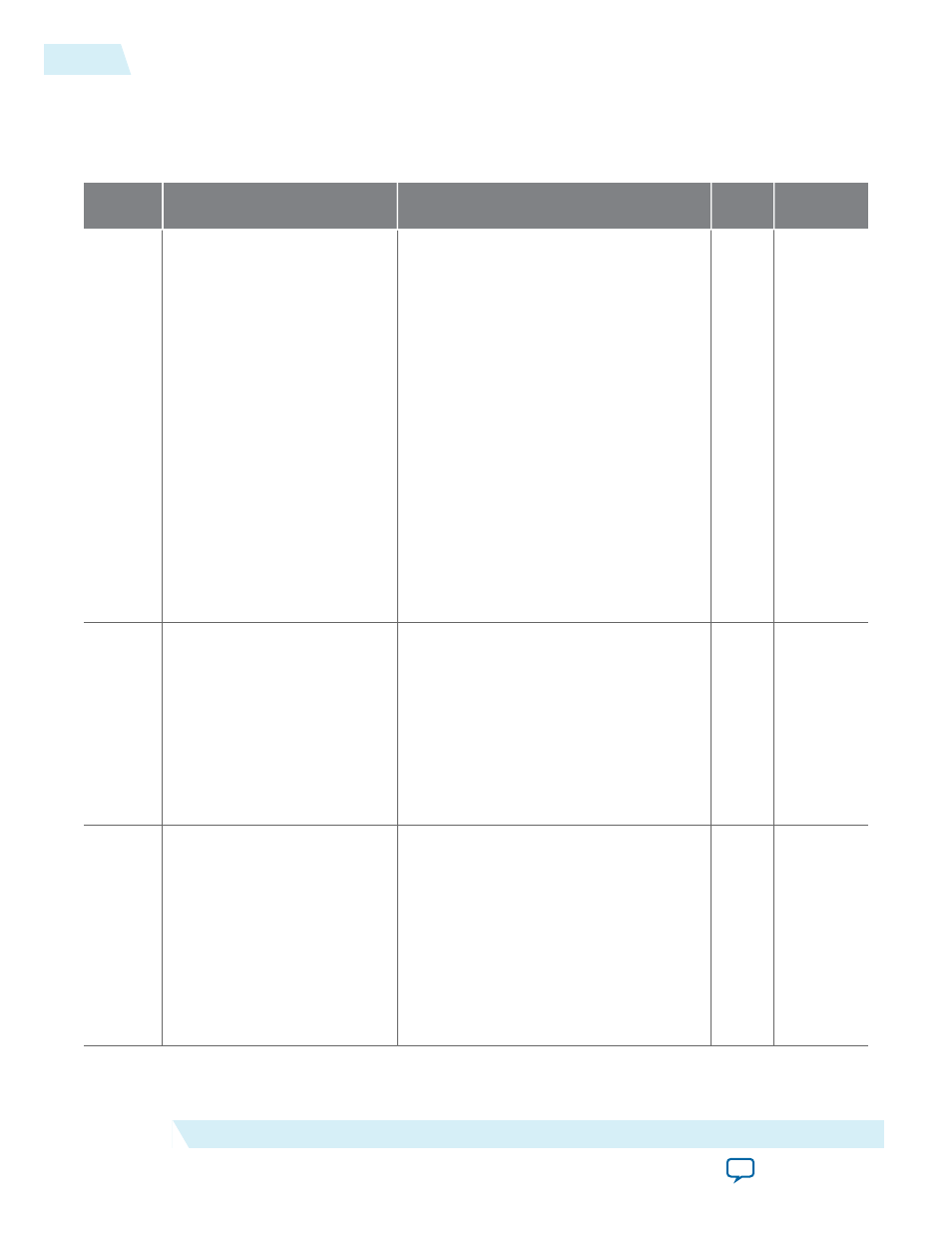

Table 4-7: Flow Control Registers

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0040

tx_pauseframe_control

• Bits 1:0—configures the transmission of

pause frames.

00: No pause frame transmission.

01: Trigger the transmission of an XON

pause frame (pause quanta = 0), if the

transmission is not disabled by other

conditions.

10: Trigger the transmission of an XOFF

pause frame (pause quanta =

tx_

pauseframe_quanta

register), if the

transmission is not disabled by other

conditions.

11: Reserved. This setting does not

trigger any action.

• Bits 31:2—reserved.

Changes to this self-clearing register affects

the next transmission of a pause frame.

RW

0x0

0x0042

tx_pauseframe_quanta

• Bits 15:0—pause quanta in unit of

quanta, 1 unit = 512 bits time. The MAC

IP core uses this value when it generates

XOFF pause frames. An XOFF pause

frame with a quanta value of 0 is

equivalent to an XON frame.

• Bits 31:16—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

0x0043

tx_pauseframe_holdoff_

quanta

• Bits 15:0—specifies the gap between two

consecutive transmissions of XOFF

pause frames in unit of quanta, 1 unit =

512 bits time. The gap prevents back-to-

back transmissions of pause frames,

which may affect the transmission of

data frames.

• Bits 31:16—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x1

4-10

Flow Control Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC