Related information – Altera Low Latency Ethernet 10G MAC User Manual

Page 25

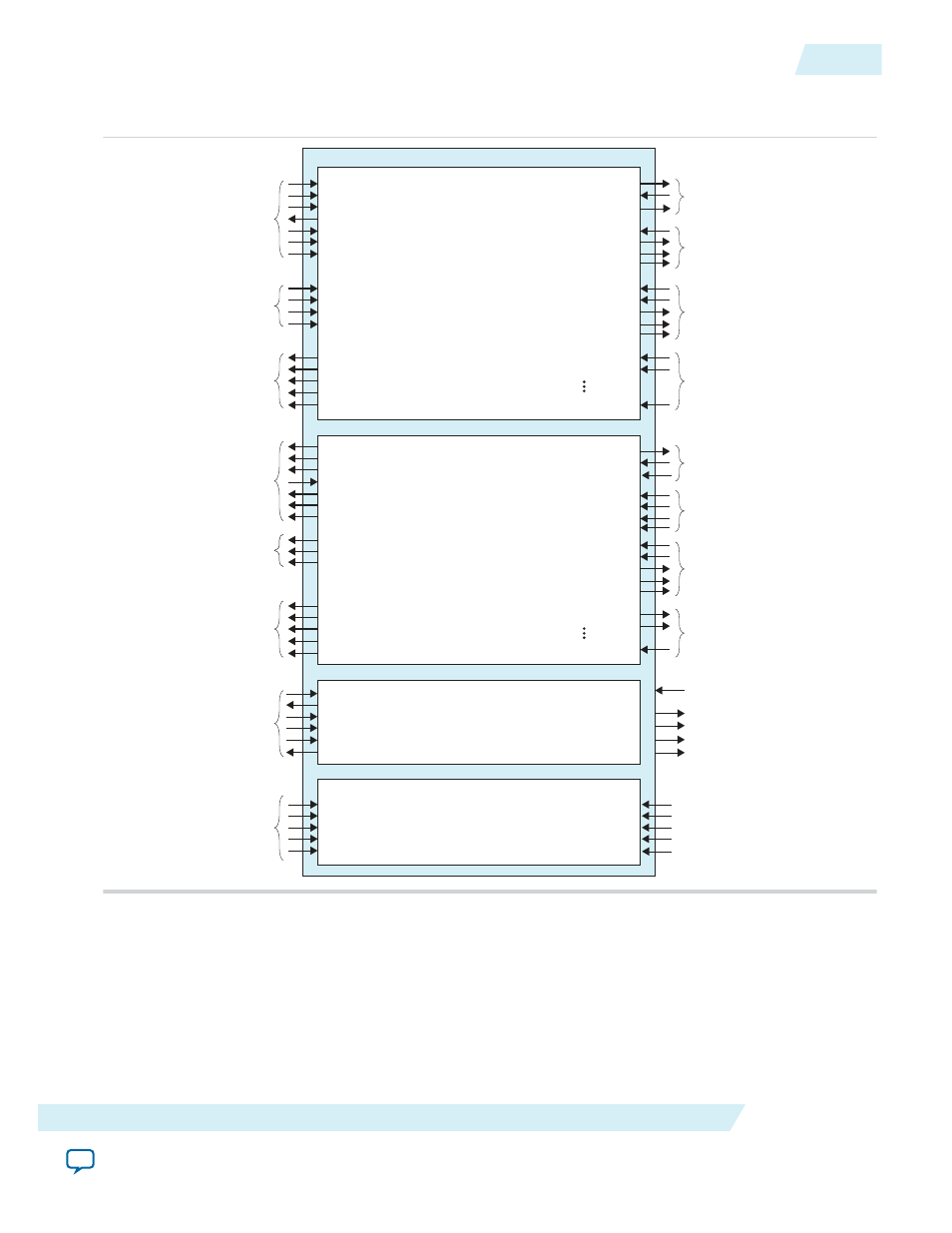

Figure 3-2: Interface Signals

The inclusion and width of some signals depend on the operating mode and features selected.

MAC RX

Clock and

Reset

csr_clk

csr_rst_n

tx_312_5_clk

tx_156_25_clk

rx_156_25_clk

rx_rst_n

tx_rst_n

rx_312_5_clk

Avalon-MM

Control and

Status Interface

csr_read

csr_readdata[31:0]

csr_write

csr_writedata[31:0]

csr_address[12:0]

csr_waitrequest

XGMII Transmit

MAC TX

xgmii_tx_data[31:0]

link_fault_status_xgmii_tx_data[1:0]

GMII Transmit

(1G/10Gbps, multi-speed)

gmii_tx_clk

gmii_tx_d[7:0]

gmii_tx_en

gmii_tx_err

MII Transmit

(multi-speed)

tx_clkena

tx_clkena_half_rate

mii_tx_d[3:0]

mii_tx_en

mii_tx_err

Avalon-ST Transmit

Data Interface

avalon_st_tx_startofpacket

avalon_st_tx_endofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_error

avalon_st_tx_data[31:0]

avalon_st_tx_empty[1:0]

Avalon-ST Transmit

Flow Control Interface

avalon_st_pause_data[1:0]

avalon_st_tx_pause_length_valid

avalon_st_tx_pause_length_data[15:0]

avalon_st_tx_pfc_gen_data[n]

Avalon-ST Transmit

Status Interface

avalon_st_txstatus_valid

avalon_st_txstatus_data[39:0]

avalon_st_txstatus_error[6:0]

avalon_st_tx_pfc_status_valid

avalon_st_tx_pfc_status_data[n]

IEEE 1588v2

Interface

tx_egress_timestamp_request_valid

tx_egress_timestamp_request_fingerprint[n]

tx_path_delay_10g_data[15:0]

xgmii_rx_data[31:0]

link_fault_status_xgmii_rx_data[1:0]

XGMII Receive

gmii_rx_clk

gmii_rx_d[7:0]

gmii_rx_dv

gmii_rx_err

GMII Receive

(1G/10Gbps, multi-speed)

rx_clkena

rx_clkena_half_rate

mii_rx_d[3:0]

mii_rx_dv

mii_rx_err

MII Receive

(multi-speed)

avalon_st_rx_startofpacket

avalon_st_rx_endofpacket

avalon_st_rx_valid

avalon_st_rx_ready

avalon_st_rx_error[5:0]

avalon_st_rx_data[31:0]

avalon_st_rx_empty[1:0]

Avalon-ST Receive

Data Interface

avalon_st_rx_pause_length_valid

avalon_st_rx_pause_length_data[15:0]

avalon_st_rx_pfc_pause_data[n]

Avalon-ST

Receive Flow

Control Interface

avalon_st_rxstatus_valid

avalon_st_rxstatus_data[39:0]

avalon_st_rxstatus_error[6:0]

avalon_st_rx_pfc_status_valid

avalon_st_rx_pfc_status_data[n]

Avalon-ST Receive

Status Interface

rx_ingress_timestamp_96b_data[95:0]

rx_ingress_timestamp_96b_valid

rx_path_delay_10g_data[15:0]

IEEE 1588v2

Time-Stamp

Interface

speed_sel

ecc_err_det_corr

ecc_err_det_uncorr

tx_xcvr_clk

rx_xcvr_clk

xgmii_tx_control[3:0]

unidirectional_en

unidirectional_remote_fault_dis

LL Ethernet 10G MAC

Avalon-MM

Control and Reset

xgmii_rx_control[3:0]

Related Information

Interface Signals for LL Ethernet 10G MAC

on page 5-1

Describes each signal in detail.

UG-01144

2014.12.15

Interfaces

3-3

Functional Description of LL Ethernet 10G MAC

Altera Corporation