Altera Low Latency Ethernet 10G MAC User Manual

Page 109

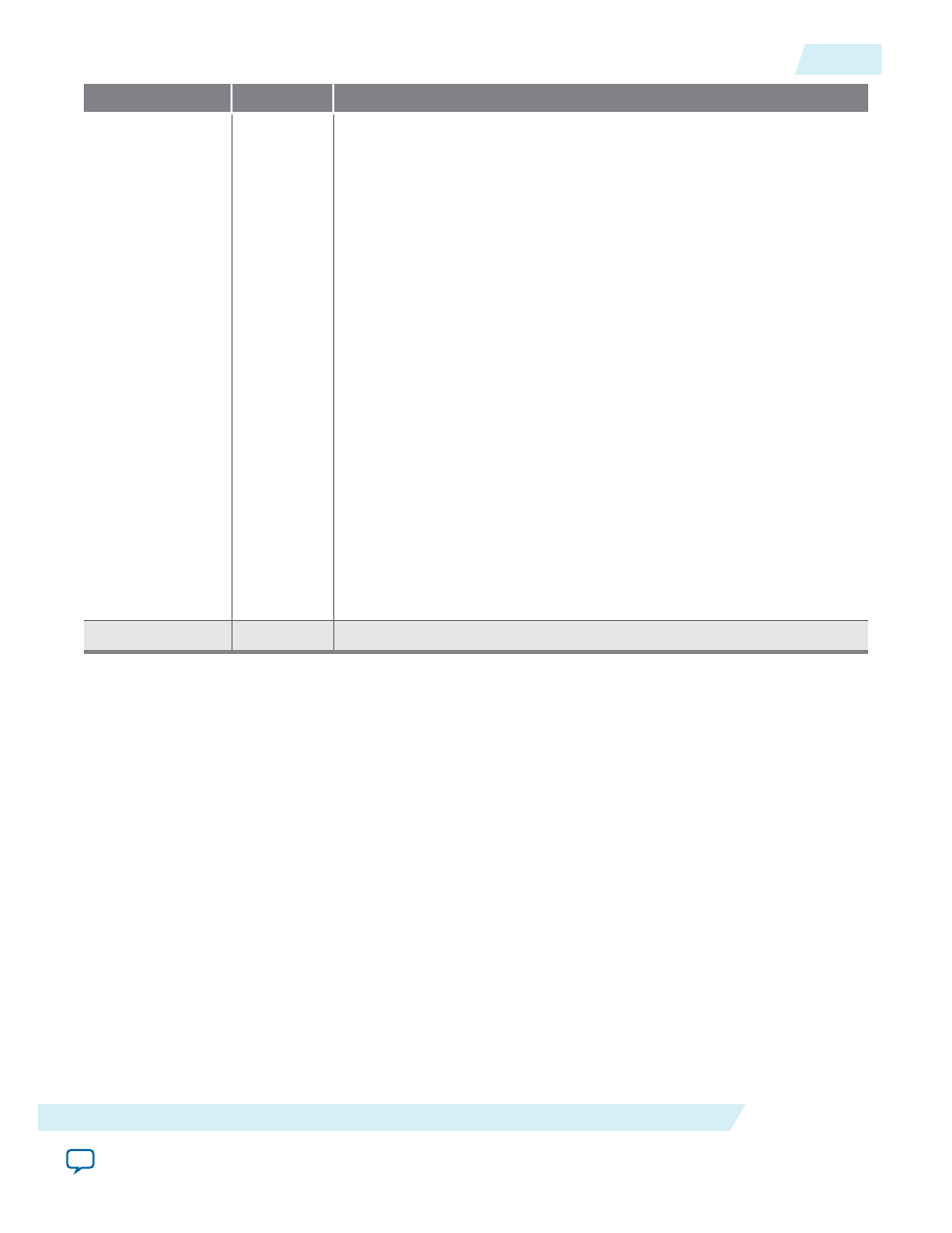

Date

Version

Changes

June 2014

2014.06.30 • Improved the performance and resource utilization.

• Added a new feature—Unidirectional Ethernet.

• Added a new parameter—Enable Unidirectional feature.

• Added Unidirectional registers and signals.

• Added information about PMA analog and digital delay for IEEE

1588v2 MAC registers.

• Edited the bit description of

avalon_st_rxstatus_error[]

signal.

• Added more information about the

avalon_st_pause_data[0]

bit

signal to indicate that the transmission of XON pause frames only

trigger for one time after XOFF pause frames regardless of how long

the

avalon_st_pause_data[0]

is asserted.

• Updated the statistics registers description.

• Edited the bit description of

tx_underflow_counter0, tx_

underflow_counter1, rx_pktovrflow_etherStatsDropE-

vents,rx_pktovrflow_error

signals.

• Edited the bit description of

csr_clk

signal to state that the

recommended clock frequency for this signal is 125 Mhz–156.25 Mhz

regardless of whether you select register-based or memory-based

statistics counter.

• Updated the

tx_rst_n

and

rx_rst_n

signals description to reflect the

change from asynchronous reset to synchronous reset.

• Updated the

csr_waitrequest

signal description.

December 2013

2013.12.02 Initial release

UG-01144

2014.12.15

Low Latency Ethernet 10G MAC User Guide Document Revision History

A-3

Additional Information

Altera Corporation