Functional description of ll ethernet 10g mac, Architecture, Functional description of ll ethernet 10g mac -1 – Altera Low Latency Ethernet 10G MAC User Manual

Page 23: Architecture -1

Functional Description of LL Ethernet 10G MAC

3

2014.12.15

UG-01144

The Low Latency (LL) Ethernet 10G MAC IP core handles the flow of data between a client and an

Ethernet network through an Ethernet PHY. On the transmit path, the MAC IP core accepts client frames

and constructs Ethernet frames by inserting various control fields, such as checksums before forwarding

them to the PHY. Similarly, on the receive path, the MAC accepts Ethernet frames via a PHY, performs

checks, and removes the relevant fields before forwarding the frames to the client. You can configure the

MAC IP core to collect statistics on both transmit and receive paths.

Architecture

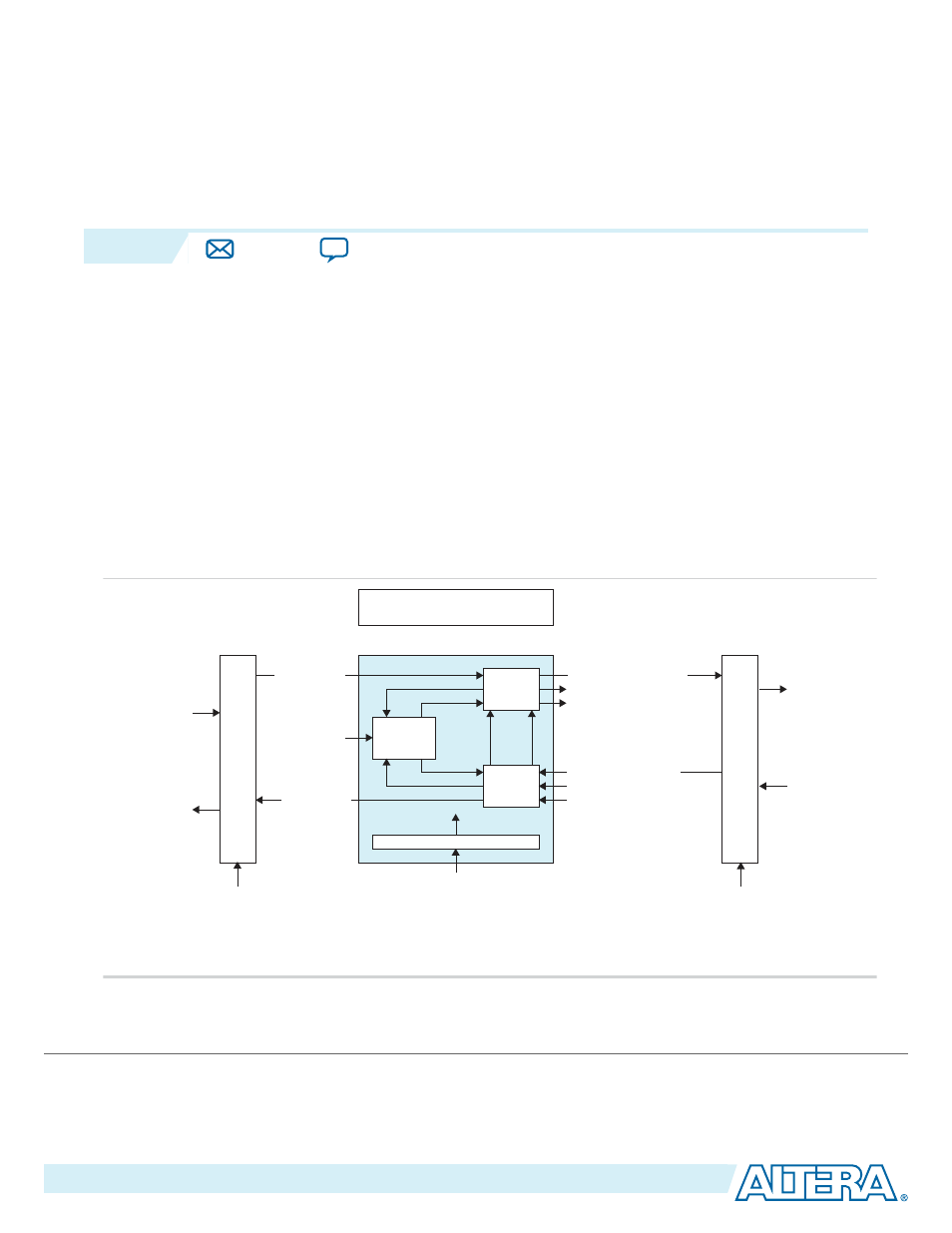

The LL Ethernet 10G MAC IP core is a composition of the following blocks: MAC receiver (MAC RX),

MAC transmitter (MAC TX), configuration and status registers, and clock and reset.

Figure 3-1: LL Ethernet 10G MAC Block Diagram

MAC TX

Control & Status

Registers

MAC RX

Clock & Reset

LL Ethernet 10G MAC

CSR Adapter

(Optional)

Av

alon-ST 32/64b A

dapt

er

(O

ptional)

XGMII SDR 32/64b A

dapt

er

(O

ptional)

32-Bit XGMII Transmit Interface

8-Bit GMII Transmit Interface

4-Bit MII Transmit Interface

32-Bit XGMII Receive Interface

8-Bit GMII Receive Interface

4-Bit MII Receive Interface

64-Bit XGMII

Receive Interface

64-Bit XGMII

Transmit Interface

64-Bit XGMII

Receive Interface

64-Bit XGMII

Transmit Interface

Flow

Control

Link

Fault

Respective

Domains

Clock & Reset

Signals

Clock & Reset

Signals

Clock & Reset

Signals

32-Bit Avalon-ST

Transmit Interface

32-Bit Avalon-MM

Interface

32-Bit Avalon-ST

Receive Interface

Notes:

(1) Applies to 1G/10G and Multi Speed MAC only.

(2) Applies to Multi Speed MAC only.

(1)

(1)

(2)

(2)

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134