Supported phys, Supported phys -21 – Altera Low Latency Ethernet 10G MAC User Manual

Page 43

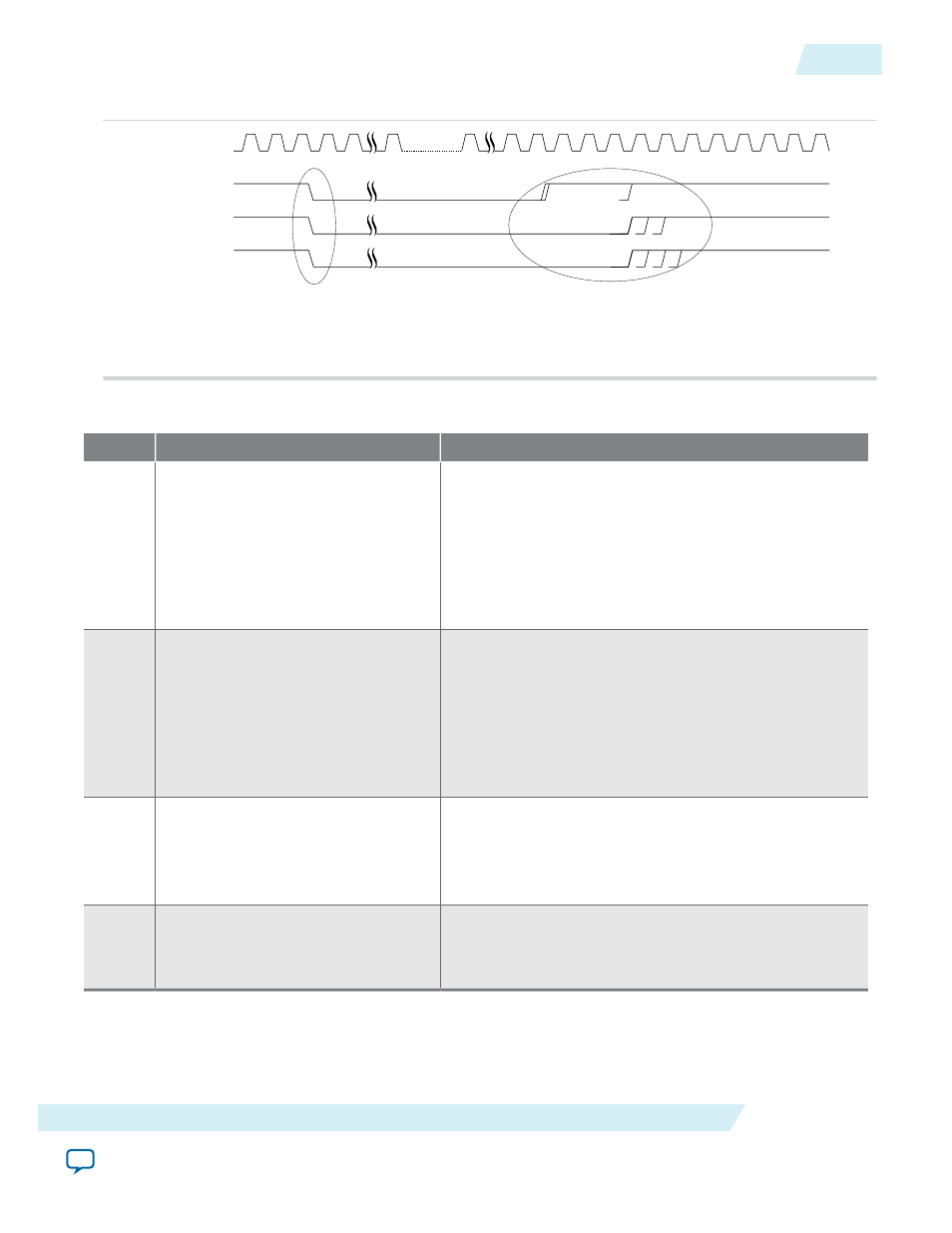

Figure 3-18: CSR Reset

csr, tx, rx clocks

csr_rst_n

tx_rst_n

rx_rst_n

When you assert csr_rst_n

, you must

also assert tx_rst_n

and rx_rst_n

.

Hold the reset signals active for at least 3 clock

periods of the slowest clock.

Deassert csr_rst_n

no later than

tx_rst_n

and rx_rst_n

.

You can configure the registers after csr_rst_n

is deasserted, but before data transfer begins.

Table 3-3: TX and RX Datapaths Reset

No

Stage

Steps

1

Ensure no data transfer in progress.

1. Set the

tx_packet_control[0]

bit to 1 to disable the

TX datapath; the

rx_transfer_control[0]

bit to

disable the RX datapath.

2. Check the

tx_transfer_status[8]

bit for a value of

0 to ensure that no TX data transfer is in progress; the

rx_transfer_status[8]

bit for RX path. Alterna‐

tively, wait for a period of time.

2

Trigger reset.

1. Assert the

tx_rst_n

signal or the

rx_rst_n

signal to

reset the MAC TX or MAC RX respectively. You can

also trigger the reset by setting the

mac_reset_

control[0]

bit or the

mac_reset_control[8]

bit to

1 to reset the MAC TX or MAC RX respectively.

2. Hold the reset signal active for at least three clock

cycles.

3

Stop reset.

1. Release the reset signal only when the clocks are

stable.

2. Wait for 500 ns to ensure the reset is fully complete.

3. Clear the statistics counters.

4

Resume data transfer.

1. Clear the

tx_packet_control[0]

bit to enable the

TX datapath; the

rx_transfer_control[0]

bit to

enable the RX datapath.

Supported PHYs

You can connect the LL 10GbE MAC IP core to a PHY IP core using XGMII, GMII, or MII interfaces.

UG-01144

2014.12.15

Supported PHYs

3-21

Functional Description of LL Ethernet 10G MAC

Altera Corporation