Altera Low Latency Ethernet 10G MAC User Manual

Page 61

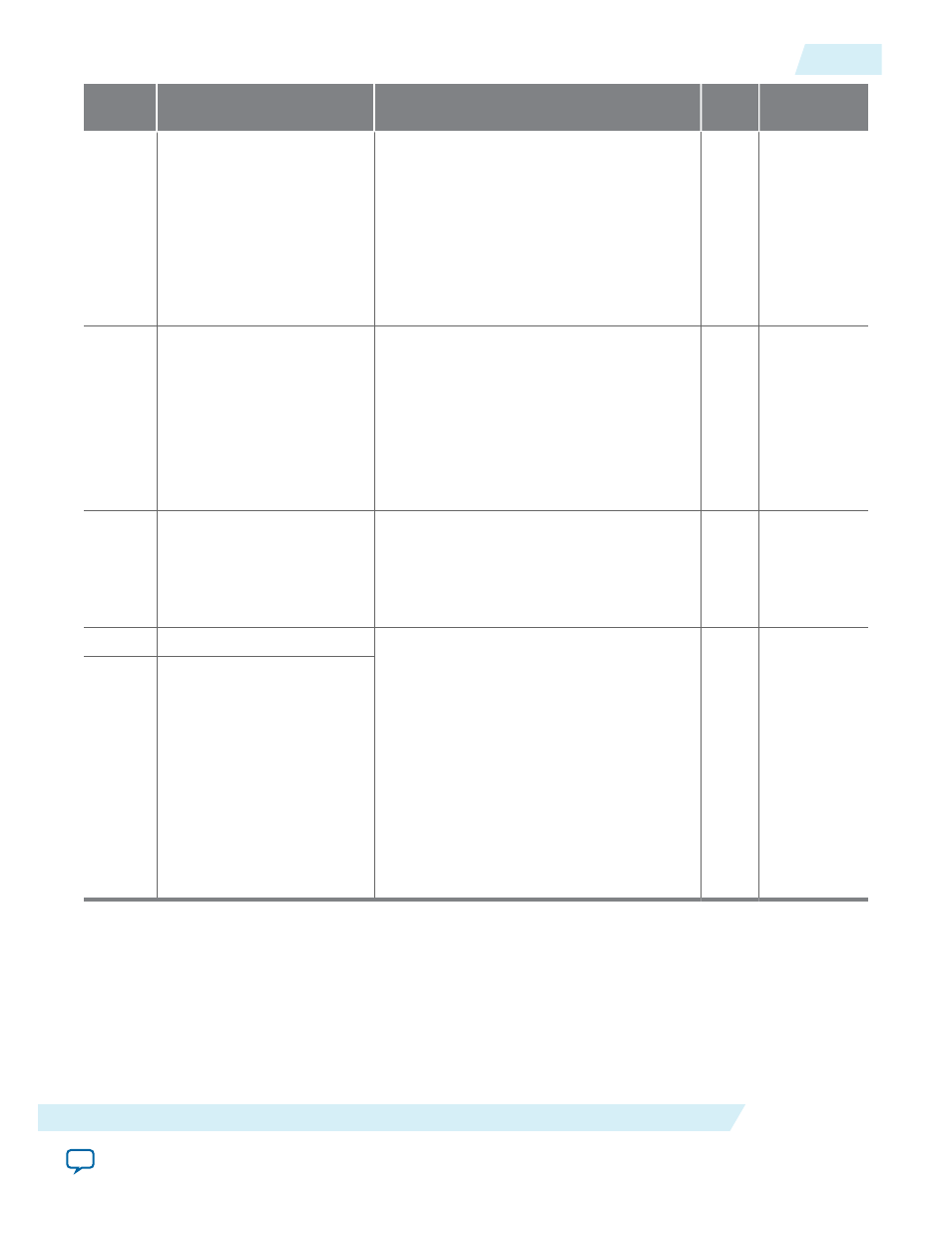

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x002D

tx_vlan_detection

• Bit 0—TX VLAN detection disable.

0: The MAC detects VLAN and stacked

VLAN frames.

1: The MAC does not detect VLAN and

stacked VLAN frames. When received, the

MAC treats them as basic frames and

considers their tags as payload bytes.

• Bits 31:1—reserved.

RW

0x0

0x002E

tx_ipg_10g

• Bit 0—use this bit to specify the average

IPG for operating speed of 10 Gbps.

0: Sets the average IPG to 8 bytes.

1: Sets the average IPG to 12 bytes.

• Bits 31:1—reserved.

The Unidirectional feature does not support

an average IPG of 8 bytes.

RW

0x0

0x002F

tx_ipg_10M_100M_1G

• Bits 3:0—use these bits to specify the

average IPG for operating speed of 10

Mbps, 100 Mbps or 1 Gbps. Valid values

are between 8 to 15 bytes.

• Bits 31:4—reserved.

RW

0x0

0x003E

tx_underflow_counter0

36-bit error counter that collects the number

of truncated TX frames when TX buffer

underflow persists.

•

tx_underflow_counter0

: Lower 32 bits of

the error counter.

•

tx_underflow_counter1[3:0]

: Upper 4

bits of the error counter.

•

tx_underflow_counter1[31:4]

—

reserved.

To read the counter, read the lower 32 bits

followed by the upper 4 bits. The IP core

clears the counter after a read.

RO

0x0

0x003F

tx_underflow_counter1

UG-01144

2014.12.15

TX_Configuration and Status Registers

4-9

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation