Avalon-st rx status signals, Avalon-st rx status signals -10 – Altera Low Latency Ethernet 10G MAC User Manual

Page 92

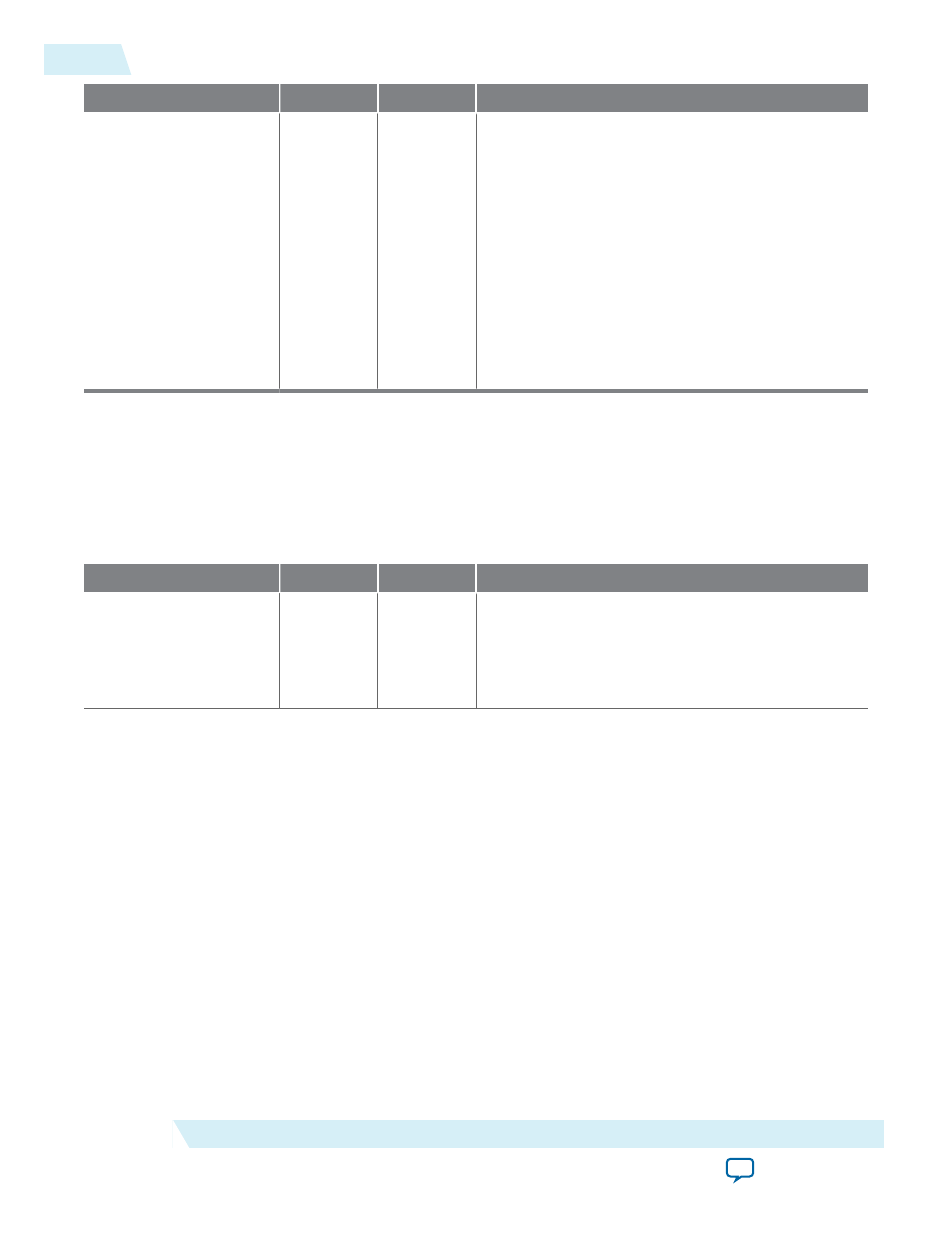

Signal

Direction

Width

Description

avalon_st_tx_pfc_

status_data[]

Out

n

(4 - 16)

n = 2 x Number of PFC queues parameter

When set to 1, the respective bit indicates the

following flow control request to the remote

partner.

• Bit 0: XON request for priority queue 0.

• Bit 1: XOFF request for priority queue 0.

• Bit 2: XON request for priority queue 1.

• Bit 3: XOFF request for priority queue 1.

• Bit 4: XON request for priority queue 2.

• Bit 5: XOFF request for priority queue 2.

• .. and so forth.

Related Information

on page 3-14

Describes how the MAC IP core checks the frame and payload lengths.

Avalon-ST RX Status Signals

Table 5-10: Avalon-ST RX Status Signals

Signal

Direction

Width

Description

avalon_st_rxstatus_

valid

Out

1

When asserted, this signal qualifies the

avalon_st_

rxstatus_data[]

and

avalon_st_rxstatus_

error[]

signals. The MAC IP core asserts this

signal in the same clock cycle the

avalon_st_rx_

endofpacket

signal is asserted.

5-10

Avalon-ST RX Status Signals

UG-01144

2014.12.15

Altera Corporation

Interface Signals for LL Ethernet 10G MAC