Ecc registers, Ecc registers -24 – Altera Low Latency Ethernet 10G MAC User Manual

Page 76

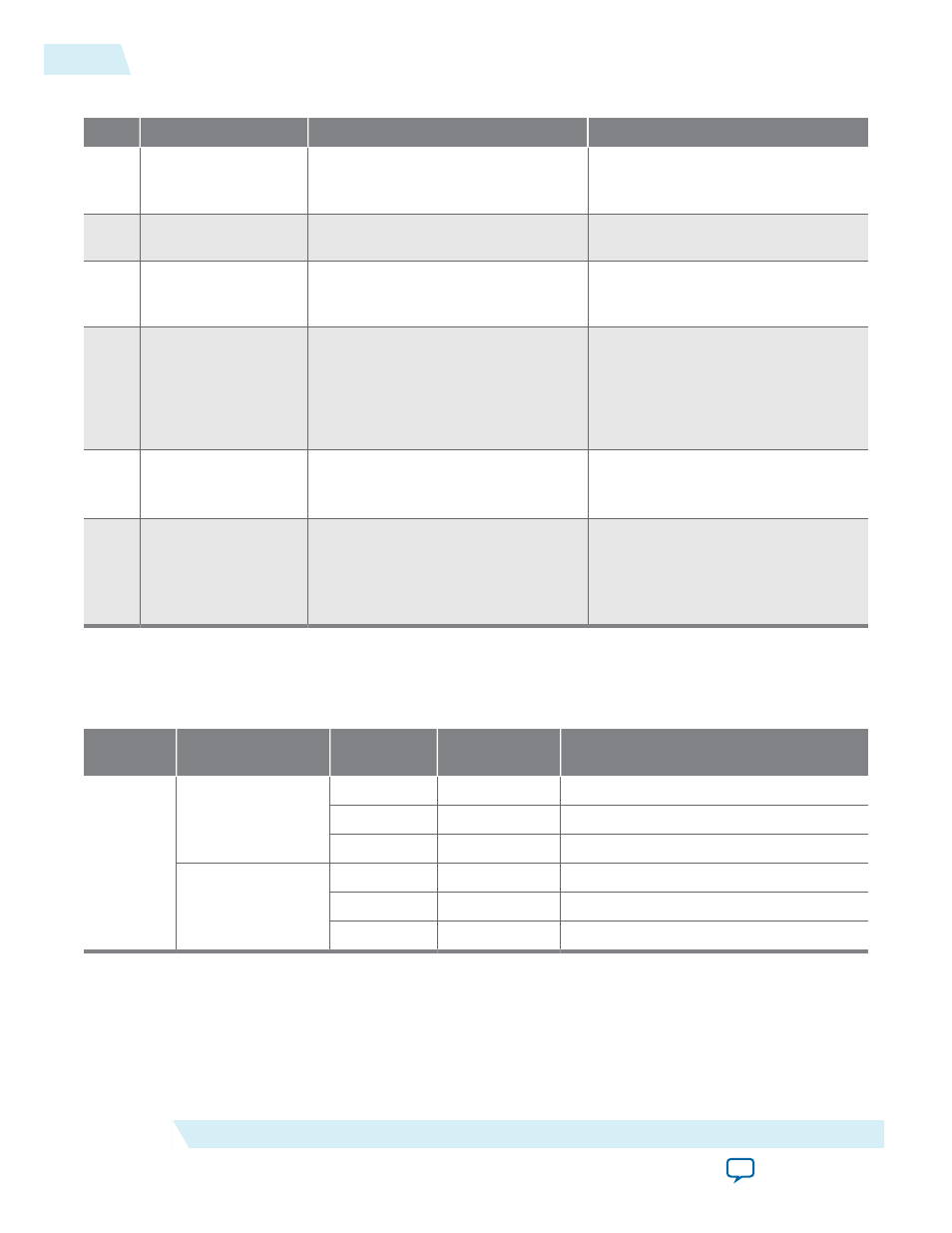

Table 4-16: Example: Calculating Timing Adjustments for 10M – 10GbE Design in Stratix V Device

Step

Description

10G

10M, 100M or 1G

1

Identify the digital

latency for the device.

For Stratix V using the PMA mode of

40 bits, the digital latency is 87 UI.

For Stratix V using the PMA mode

of 10 bits, the digital latency is 26

UI.

2

Convert the digital

latency in UI to ns.

87 UI * 0.097 = 8.439 ns

26 UI * 0.8 = 20.8 ns

3

Add the analog latency

to the digital latency in

ns.

8.439 ns + 1.75 ns = 10.189 ns

20.8 ns + 1.75 ns = 22.55 ns

4

Add any external PHY

delay to the total

obtained in step 3. In

this example, an

external PHY delay of

1 ns is assumed.

10.189 ns + 1 ns = 11.189 ns

22.55 ns + 1 ns = 23.55 ns

5

Convert the total

latency to ns and fns

in hexadecimal.

ns: 0xB

fns: 0.189 * 65536 = 0x3062

ns: 0x17

fns: 0.55 * 65536 = 0x8CCC

6

Configure the

respective registers.

rx_ns_adjustment_10G

= 0xB

rx_fns_adjustment_10G

= 0xD4BC

rx_ns_adjustment_mult_speed

=

0x17

rx_fns_adjustment_mult_speed

= 0x4CCC

The Quartus II simulation model is cycle accurate for the PCS, but not for the PMA. The latency values

reported are therefore different from the hardware.

Table 4-17: PMA Delay from Simulation Model

Delay

Device

PMA Mode

(bit)

Latency

MAC Configurations

Digital

Arria V GZ and

Stratix V

40

150.5 UI

10GbE or 10G of 10M-10GbE

32

196 UI

10GbE

10

33.5 UI

1G/100M/10M of 10M-10GbE

Arria 10

40

65.5 UI

10GbE or 10G of 10M-10GbE

32

57.5 UI

10GbE or 10G of 10M-10GbE

10

23.5 UI

1G/100M/10M of 10M-10GbE

ECC Registers

The ECC registers are used when you turn on Enable ECC on memory blocks. They are reserved when

not used.

4-24

ECC Registers

UG-01144

2014.12.15

Altera Corporation

Configuration Registers for LL Ethernet 10G MAC