Altera Low Latency Ethernet 10G MAC User Manual

Page 63

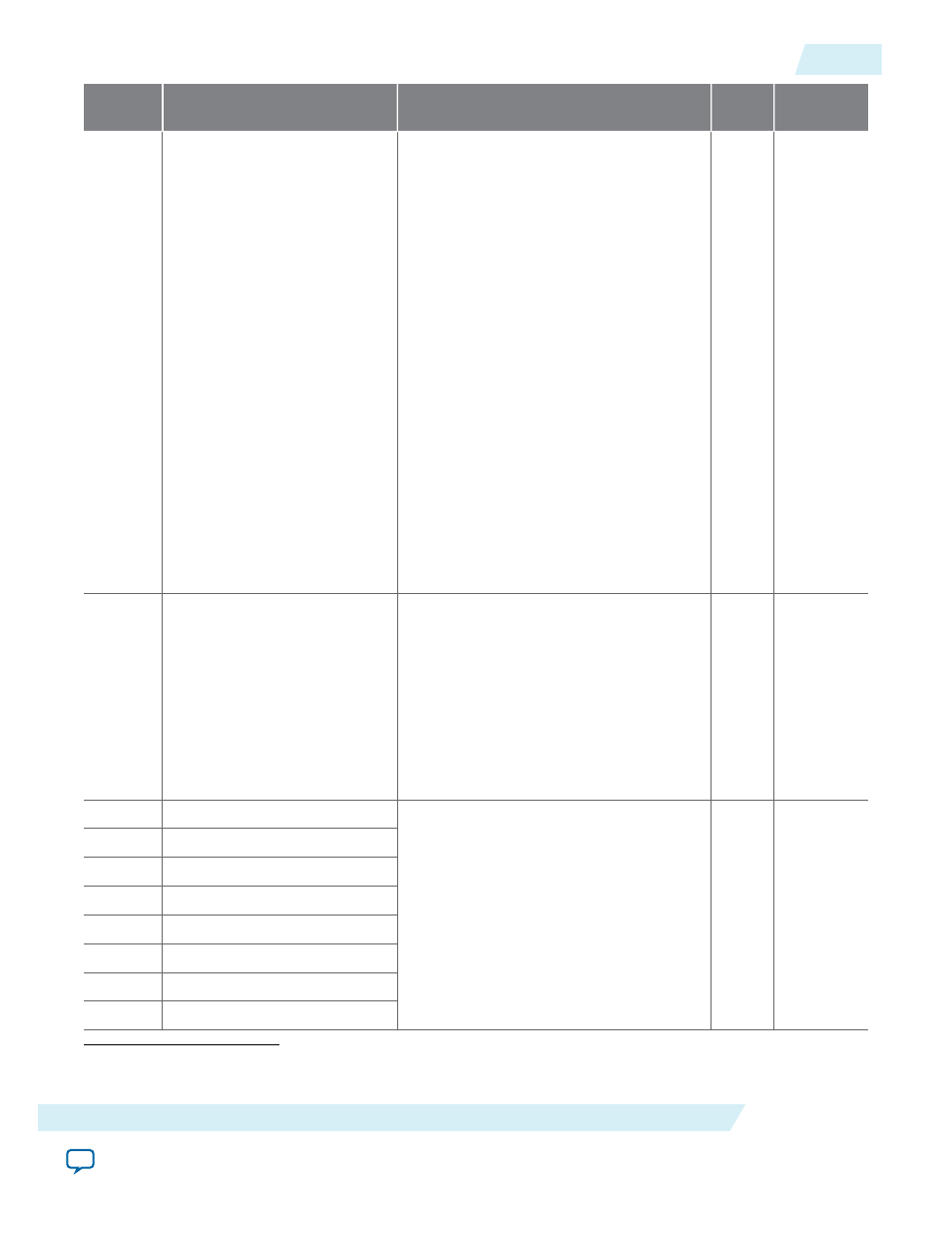

Word

Offset

Register Name

Description

Access

HW Reset

Value

0x0044

tx_pauseframe_enable

• Bit 0—configures the transmission of

pause frames. This bit affects pause

frame requests from both register and

vector settings.

0: Disables pause frame transmission.

1: Enables pause frame transmission, if

TX path is enabled by

tx_packet_

control

.

• Bits 2:1—specifies the trigger for pause

frame requests.

00: Accepts pause frame requests only

from vector setting,

avalon_st_pause_

data

.

01: Accepts pause frame requests only

from register setting,

tx_pauseframe_

control

.

10 / 11: Reserved.

• Bits 31:3—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x1

0x0046

tx_pfc_priority_enable

(5)

Enables priority-based flow control on the

TX datapath.

• Bits 7:0—setting bit n enables priority-

based flow control for priority queue n.

For example, setting

tx_pfc_priority_

enable[0]

enables queue 0.

• Bits 31:8—reserved.

Configure this register before you enable

the MAC IP core for operations.

RW

0x0

0x0048

pfc_pause_quanta_0

(5)

Specifies the pause quanta for each priority

queue.

• Bits 15:0—

pfc_pause_quanta_n[15:0]

specifies the pause length for priority

queue n in quanta unit, where 1 unit =

512 bits time.

• Bits 31:16—reserved.

Configure these registers before you enable

the MAC IP core for operations.

RW

0x0

0x0049

pfc_pause_quanta_1

(5)

0x004A

pfc_pause_quanta_2

(5)

0x004B

pfc_pause_quanta_3

(5)

0x004C

pfc_pause_quanta_4

(5)

0x004D

pfc_pause_quanta_5

(5)

0x004E

pfc_pause_quanta_6

(5)

0x004F

pfc_pause_quanta_7

(5)

(5)

This register is used only when you turn on the Enable preamble pass-through mode option. It is reserved

when not used.

UG-01144

2014.12.15

Flow Control Registers

4-11

Configuration Registers for LL Ethernet 10G MAC

Altera Corporation