Tx timing diagrams, Tx timing diagrams -9, Table 3-2: register field and link status – Altera Low Latency Ethernet 10G MAC User Manual

Page 31: Don't care

Table 3-2: Register Field and Link Status

Bit 0 Register Field Bit 1 Register Field

Link Status

TX XGMII Interface Behavior

Don't care

Don't care

No link fault

Continue to allow normal packet transmission.

0

Don't care

Local fault

Immediately override the current content with

remote fault sequence.

1

0

Local fault

Continue to send packet if there is one.

Otherwise, override the IPG/IDLE bytes with

remote fault sequence.

(1)

1

1

Local fault

Continue to allow normal packet transmission

(similar to no link fault).

0

Don't care

Remote fault

Immediately override the current content with

IDLE control characters.

1

Don't care

Remote fault

Continue to allow normal packet transmission

(similar to no link fault).

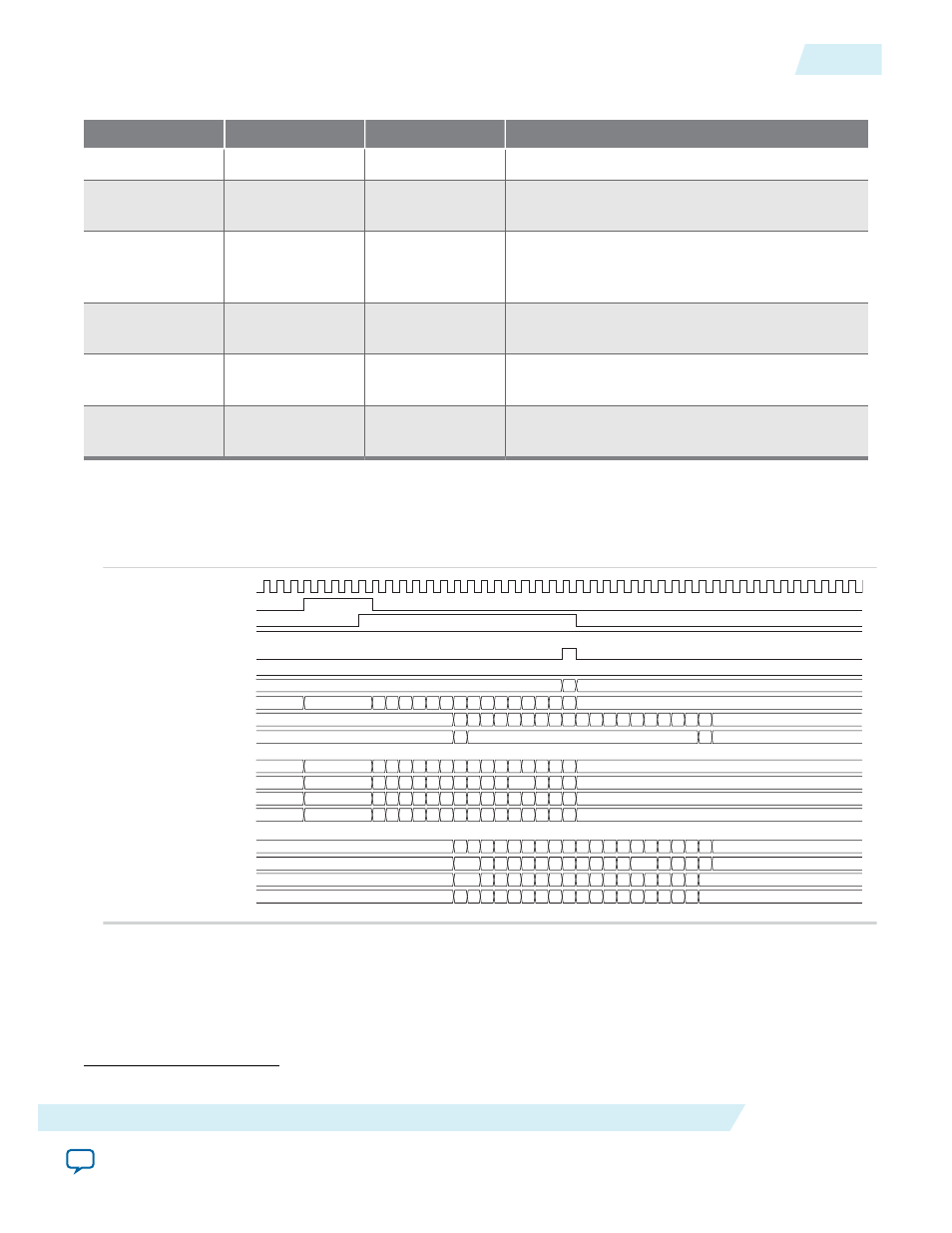

TX Timing Diagrams

Figure 3-7: Normal Frame

The following diagram shows the transmission of a normal frame.

tx_312_5_clk

avalon_st_tx_startofpacket

avalon_st_tx_valid

avalon_st_tx_ready

avalon_st_tx_endofpacket

avalon_st_tx_error

avalon_st_tx_empty[1:0]

avalon_st_tx_data[31:0]

xgmii_tx_data[31:0]

xgmii_tx_control[3:0]

avalon_st_tx_data[31:24]

avalon_st_tx_data[23:16]

avalon_st_tx_data[15:8]

avalon_st_tx_data[7:0]

xgmii_tx_data[7:0]

xgmii_tx_data[15:8]

xgmii_tx_data[23:16]

xgmii_tx_data[31:24]

0

3

0

0f8e_8236

0023_4567

*5 *1 *2 *2 *5 *b *c *7 *e *d *5 *3 *e *5 *0

cc6b_d355

0707_0707

*b *5 *0 *9 *1 *0 *c *e *b *6 *1 *0 *b *7 *6 *d *d *d *2

0707_0707

f

1

0

e

f

0f

00

89 f1 00 fc ce 6b 26 01 e0 0b 87 a6 7d 4d 5d

cc

8e

23

ab c7 2f 8c 3f 9f d9 77 59 71 e5 3a 42 00

6b

82

45

c4 e9 fb 00 62 f7 80 84 09 c5 21 65 4b b1 00

d3

36

67

d5 61 d2 82 85 4b fc 67 9e 9d 45 23 ee a5 00

55

07

7d

fb 55 00 89 f1 00 fc ce 6b 26 01 e0 0b 87 a6

07

07

3a

55 23 ab c7 2f 8c 3f 9f d9 77

71

e5

07

07

4b

55 45 c4 e9 fb 00 62 f7 80 84 09 c5 21 65

07

07

ee

55 d5 67 d5 61 d2 82 85 4b fc 67 9e 8d 45 23

07

a2

4d 5d

fd

42 13

b1 8a

a5 d0

59

(1)

At least a full column of IDLE (four IDLE characters) must precede the remote fault sequence.

UG-01144

2014.12.15

TX Timing Diagrams

3-9

Functional Description of LL Ethernet 10G MAC

Altera Corporation