Overflow handling, Rx timing diagrams, Overflow handling -16 – Altera Low Latency Ethernet 10G MAC User Manual

Page 38: Rx timing diagrams -16, Signal after the, Signal is reasserted. the error bit

Overflow Handling

When an overflow occurs on the client side, the client can backpressure the Avalon-ST receive interface

by deasserting the

avalon_st_rx_ready

signal. If an overflow occurs in the middle of frame transmission,

the MAC RX truncates the frame by sending out the

avalon_st_rx_endofpacket

signal after the

avalon_st_rx_ready

signal is reasserted. The error bit,

avalon_st_rx_error[5]

, is set to 1 to indicate

an overflow. If there is an overflow during client data reception, the current frame will get truncated. The

MAC RX will drop the remaining payload of the erroneous frame and the subsequent frames if the

overflow condition persists. The MAC RX then continues to receive data when the overflow condition

ceases.

RX Timing Diagrams

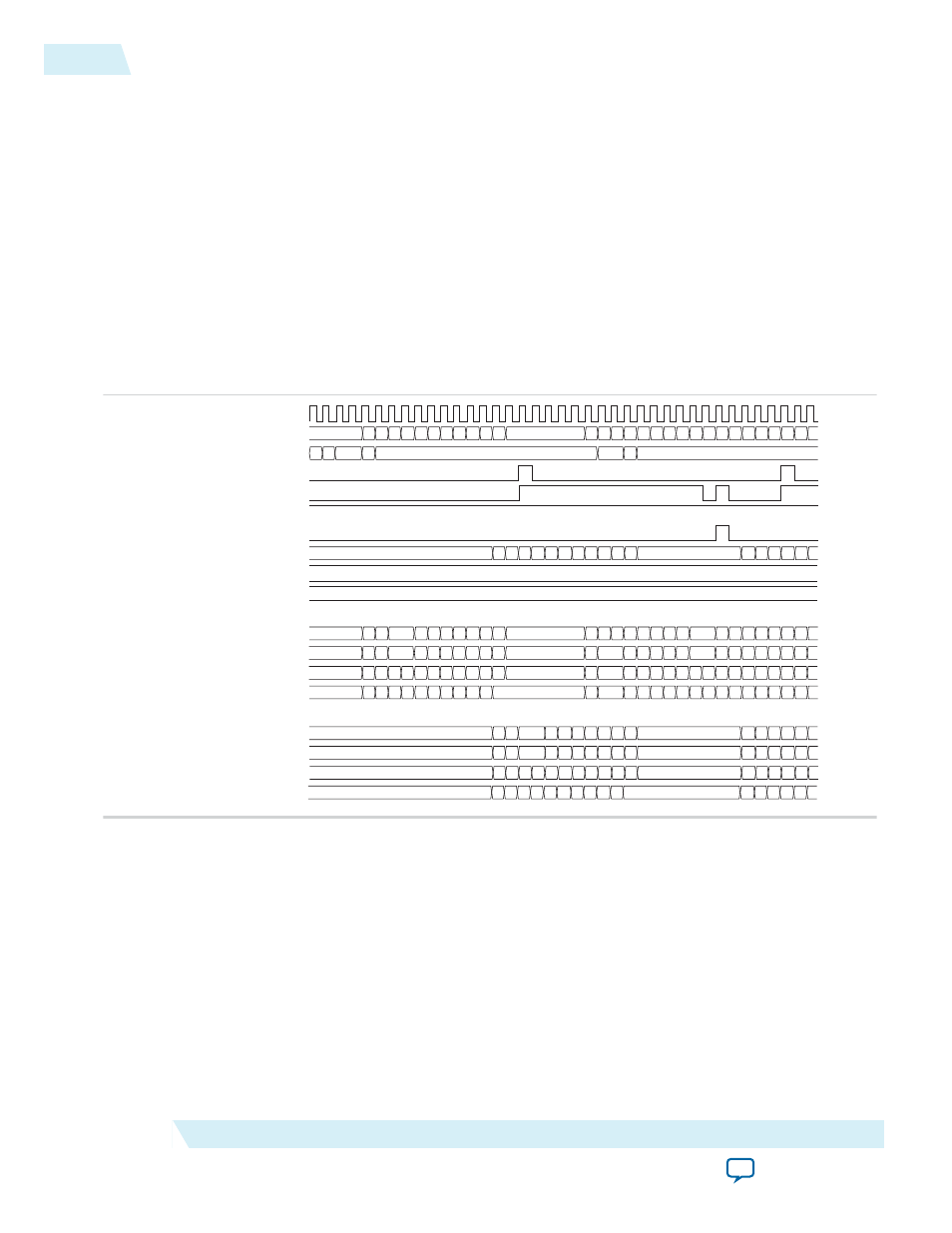

Figure 3-15: Back-to-back Transmission of Normal Frames with CRC Removal Enabled

The following diagram shows back-to-back reception of normal frames with CRC removal enabled.

rx_312_5_clk

xgmii_rx_data[31:0]

xgmii_rx_control[3:0]

avalon_st_rx_startofpacket

avalon_st_rx_valid

avalon_st_rx_ready

avalon_st_trx_endofpacket

avalon_st_rx_data[31:0]

avalon_st_rx_empty[1:0]

avalon_st_rx_error[5:0]

avalon_st_rx_data[31:24]

avalon_st_rx_data[23:16]

avalon_st_rx_data[15:8]

avalon_st_rx_data[7:0]

xgmii_rx_data[7:0]

xgmii_rx_data[15:8]

xgmii_rx_data[23:16]

xgmii_rx_data[31:24]

*

*fff

* *

* *

*c

0000_0000

*

0faa_4s5e

* *

* *

* *

*

* *

*

1 0

1

f

0

1

f

0

*

*fff *0

* *

0707_0707

*

*0

0000_0000

*

* *

*

fb

*ff

cf 88

21 22

8cc

00

fd

07

fb 3a

00 c0

0a

4d

da *

cd

3a

b6

fa

07

01

81

87

95

46

94 f2

88

ff

58 08

d3 be

88

00

07

07

88 3a

01 16

51

ae

c5 *

40

3a

df

55

80

00

f3

c7

46

df f6

88

d0 d5

cd a7

ff

00

07

07

88 3a

0a 50

51

2e

2b *

0a

3a

62

73

c2

46

97

24

43 aa

88

ad 49

f5 2a

00

07

07

88 d5

d9 6d

18

8d

57 *

7c

d5

2b

f1

00

3e

28

55

70 95

ff 61

68 03

5c 81

ff 60

fb

ff

88 b6

07

22

8c

00

07

3a 01

c0

3a

cf

f1

21

00

fb

88

ff

08 df

07

be

89

00

07

3a 80

16

3a

58

55

d3

01

88

88

d5 62

07

a7

ff

00

07

3a c2

50

3a

d0

73

cd

0a

88

ff 61

88

49 2b

07

2a

00

07

d5 00

6d

d5

ad

f1

f5

d9

88

ff 60

3-16

Overflow Handling

UG-01144

2014.12.15

Altera Corporation

Functional Description of LL Ethernet 10G MAC