2 link, 3 split – Teledyne LeCroy Summit T3-16 PCIe Multi-lane Protocol Analyzer User Manual User Manual

Page 137

Summit T3‐16 PCI Express Multi‐Lane Protocol Analyzer User Manual

125

Decoding Traffic

Teledyne LeCroy

If AER_CAP_VER = 1 and it is not a Root Port or RC Event Collector, there are 11

DWs (00h to 24h)in the total AER Capability structure.

If AER_CAP_VER = 1 and it is a Root Port or RC Event Collector, there are 14 DWs

(00h to 34h)in the total AER Capability structure.

If AER_CAP_VER = 2 then, there are 18 DWs (00h to 44h) in the total AER Capa‐

bility structure.

In fact, there are PCI‐E 3.0 compliant devices that have AER_CAP_VER=1.

Example H/W:

A PCI‐E 3.0 device that supports Multiple Header Recording, but does NOT support TLP

Prefixes. This device is allowed to have AER_CAP_VER=1, and

Multiple_Header_Recording_Capable=1

Therefore, the Teledyne Lecroy software decodes the

Multiple_Header_Recording_Capable field regardless of the value of AER_CAP_VER.

6.13.2

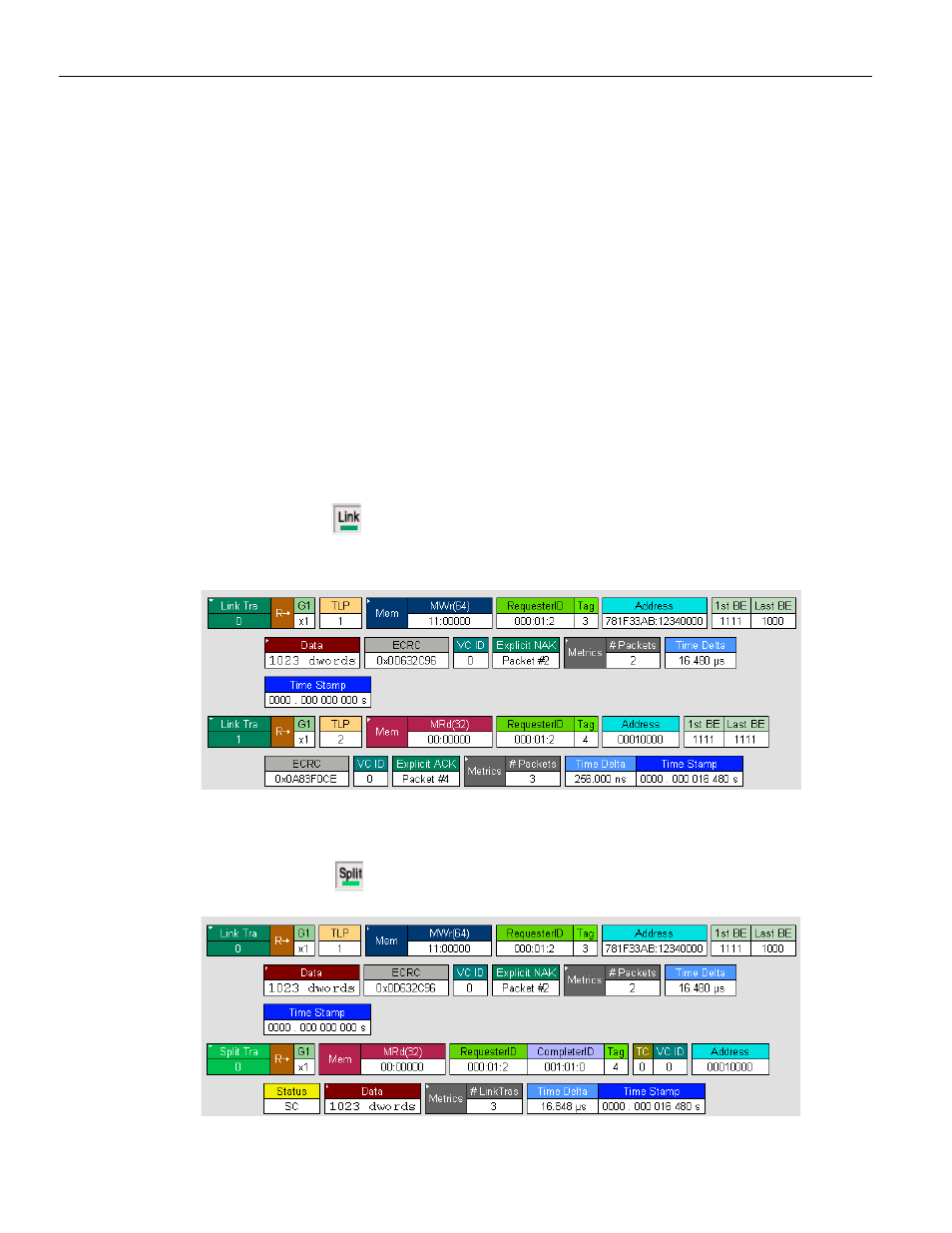

Link

Link level decode

is composed of TLP packets matched with a corresponding ACK or

NAK coming from the opposite direction.

6.13.3

Split

Split level decode

is composed of two Link transactions, the Request TLP and the

Completion TLP from the other direction.