Figure 9-2. receive dma memory organization, Figure 9-1. receive dma operation – Rainbow Electronics DS3131 User Manual

Page 78

DS3131

78 of 174

Host Actions

The host typically handles the receive DMA as follows:

1) The host is always trying to make free data buffer space available and therefore tries to fill the free-

queue descriptor.

2) The host either polls, or is interrupted, when some incoming packet data is ready for processing.

3) The host then reads the done-queue descriptor circular queue to find out which channel has data

available, what the status is, and where the receive packet descriptor is located.

4) The host then reads the receive packet descriptor and begins processing the data.

5) The host then reads the next descriptor pointer in the link-listed chain and continues this process

until either a number (from 1 to 7) of descriptors have been processed or an end of packet has been

reached.

6) The host then checks the done-queue descriptor circular queue to see if any more data buffers are

ready for processing.

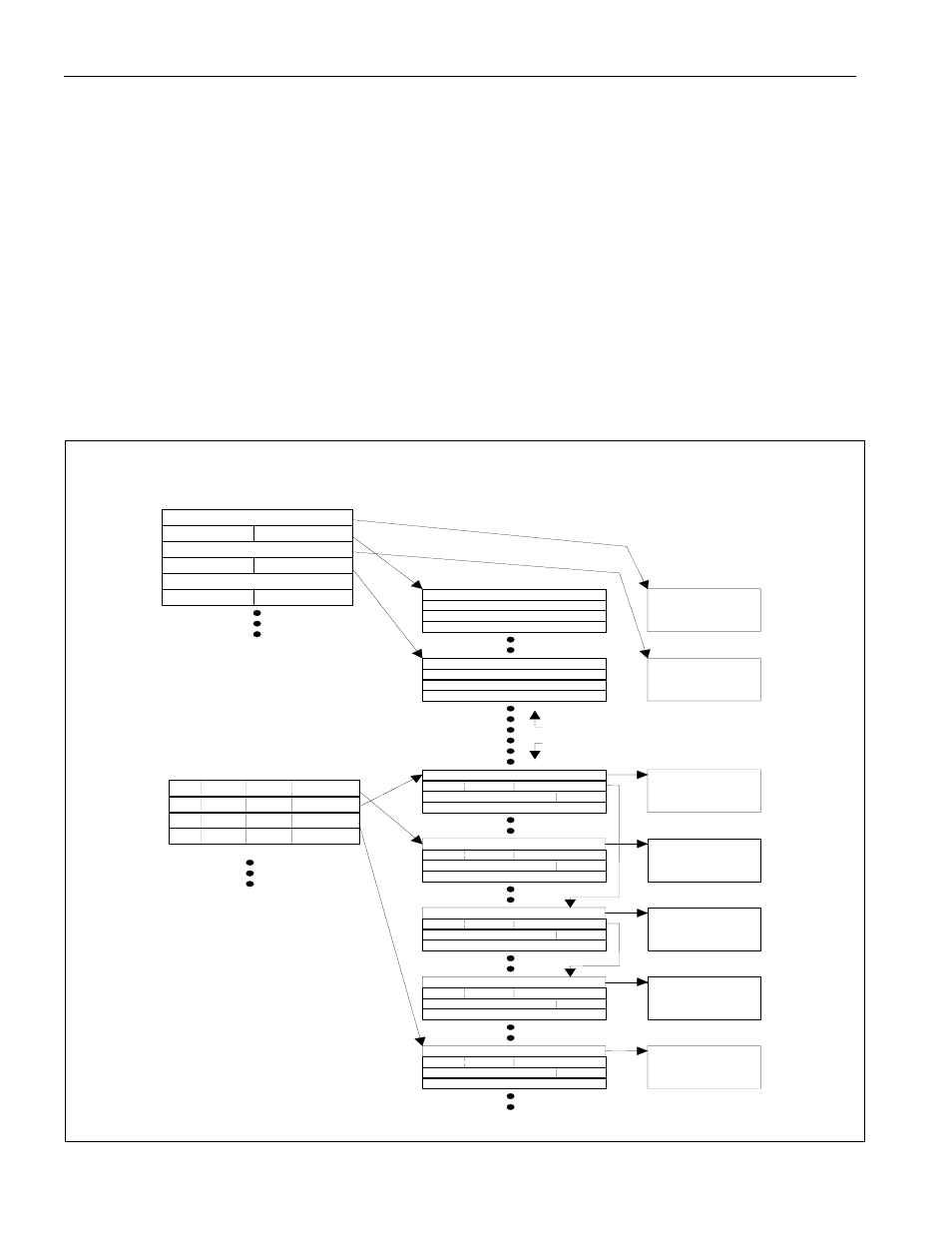

Figure 9-1. Receive DMA Operation

Free Data Buffer Address

00h

08h

10h

Free Queue Descriptors

(circular queue)

00h

04h

08h

Done Queue Descriptors

(circular queue)

Open Descriptor Space

Available for Use by the DMA

Data Buffer Address

Unused

Timestamp

CH #2

Status

0Ch

Free Data Buffer

(up to 4096 bytes)

Free Data Buffer

(up to 4096 bytes)

First Filled

Data Buffer

for Channel 2

Free Packet Descriptors & Data Buffers

Used Packet Descriptors & Data Buffers

Single Filled

Data Buffer

for Channel 5

Second Filled

Data Buffer

for Channel 2

Last Filled

Data Buffer

for Channel 2

Single Filled

Data Buffer

for Channel 9

unused

Free Desc. Ptr.

Free Desc. Ptr.

Free Desc. Ptr.

unused

unused

Free Data Buffer Address

Free Data Buffer Address

Open Descriptor Space

Available for Use by the DMA

# Bytes

Next Desc. Ptr.

Data Buffer Address

Timestamp

CH #5

Status

# Bytes

Next Desc. Ptr.

Data Buffer Address

Timestamp

CH #2

Status

# Bytes

Next Desc. Ptr.

Data Buffer Address

Timestamp

CH #2

Status

# Bytes

Next Desc. Ptr.

Data Buffer Address

Timestamp

CH #9

Status

# Bytes

Next Desc. Ptr.

EOF

Status

CH #5

Desc. Ptr.

EOF

Status

CH #2

Desc. Ptr.

EOF

Status

CH #9

Desc. Ptr.

EOF

Status

CH #

Desc. Ptr.