Lists all functions supported b, Descriptor. (see section, Table 7-c. receive bit-synchronous hdlc functions – Rainbow Electronics DS3131 User Manual

Page 60

DS3131

60 of 174

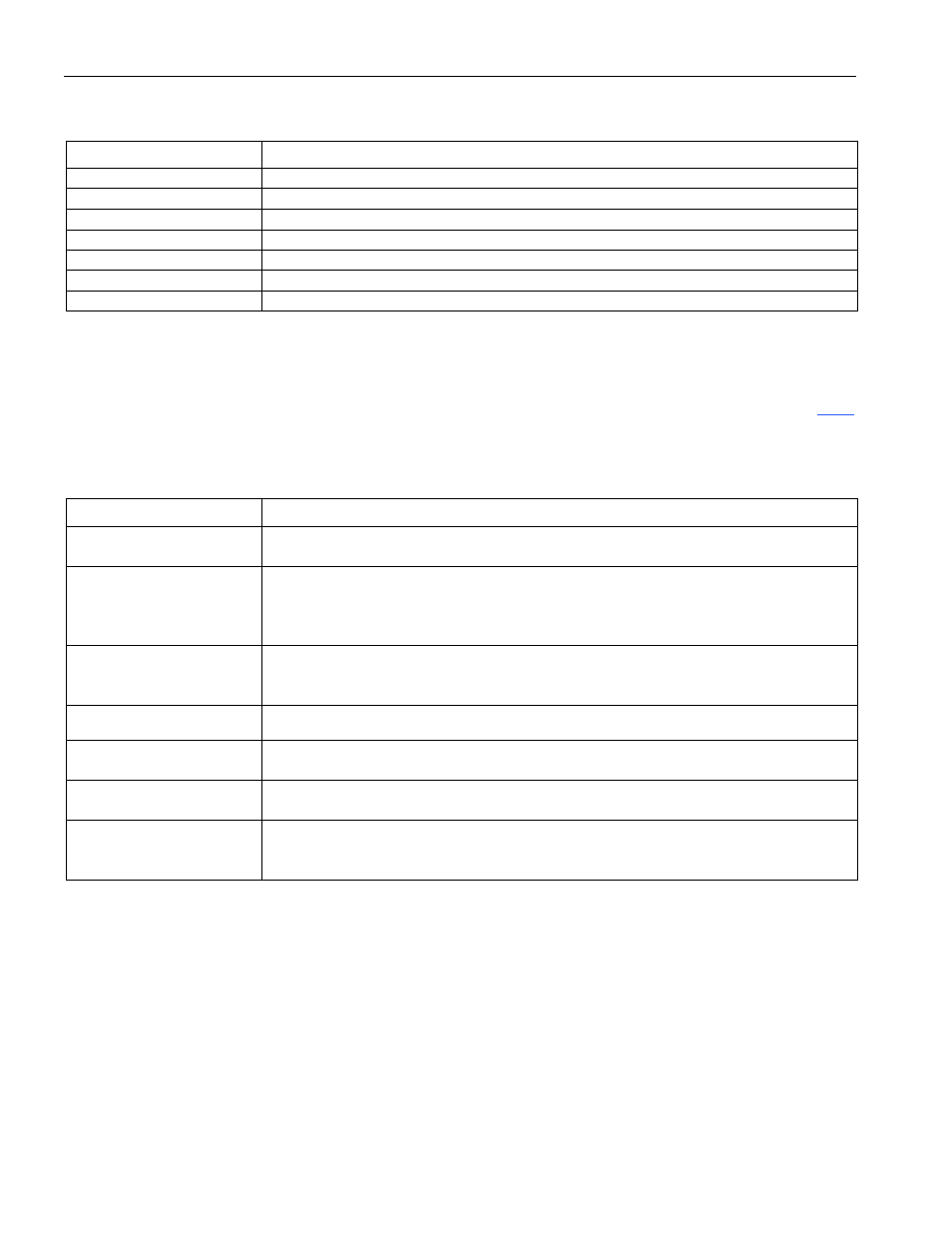

Table 7-B. Receive Bit-Synchronous HDLC Packet Processing Outcomes

OUTCOME CRITERIA

EOF/Normal Packet

Integral number of packets > min and < max is received and CRC is okay

EOF/Bad FCS

Integral number of packets > min and < max is received and CRC is bad

Abort Detected

Seven or more 1s in a row detected

EOF/Too Few Bytes

Less than the packet minimum is received (if detection enabled)

Too Many Bytes

Greater than the packet maximum is received (if detection enabled)

EOF/Bad Number of Bits

Not an integral number of bytes received

FIFO Overflow

Tried to write a byte into an already full FIFO

Note:

EOF = End of Frame, which means that this outcome is not determined until a closing flag is detected.

If any of the 40 receive HDLC channels detects an abort sequence, a FCS checksum error, or if the

packet length was incorrect, then the appropriate status bit in the status register for DMA (SDMA) is set.

If enabled, the setting of any of these statuses can cause a hardware interrupt to occur. See Section

5.3.2

for details about the operation of these status bits.

Table 7-C. Receive Bit-Synchronous HDLC Functions

Zero Destuff

This operation is disabled if the channel is set to transparent mode.

Flag Detection and Byte

Alignment

Okay to have two packets separated by only one flag or by two flags sharing 0. This

operation is disabled if the channel is set to transparent mode.

Octet Length Check

The maximum check is programmable up to 65,536 Bytes through the RHPL

register. The maximum check can be disabled through the ROLD control bit in the

RHCR register. The minimum and maximum counts include the FCS. An error is

also reported if a noninteger number of octets occur between flags.

CRC Check

Can be either set to CRC-16 or CRC-32 or none. The CRC can be passed through to

the PCI bus or not. The CRC check is disabled if the channel is set to transparent

mode.

Abort Detection

Checks for seven or more 1s in a row.

Invert Data

All data (including the flags and FCS) is inverted before HDLC processing. Also

available in the transparent mode.

Bit Flip

The first bit received becomes either the LSB (normal mode) or the MSB (telecom

mode) of the byte stored in the FIFO. Also available in the transparent mode.

Transparent Mode

If enabled, flag detection, zero destuffing, abort detection, length checking, and

FCS checking are disabled. Data is passed to the PCI bus on octet (byte) boundaries

in unchannelized operation.