Bit-synchronous hdlc register description, Fifo, Table 8-a. fifo priority algorithm select – Rainbow Electronics DS3131 User Manual

Page 61: Els within the, Table 7-d. transmit bit-synchronous hdlc functions, 3 bit-synchronous hdlc register description

DS3131

61 of 174

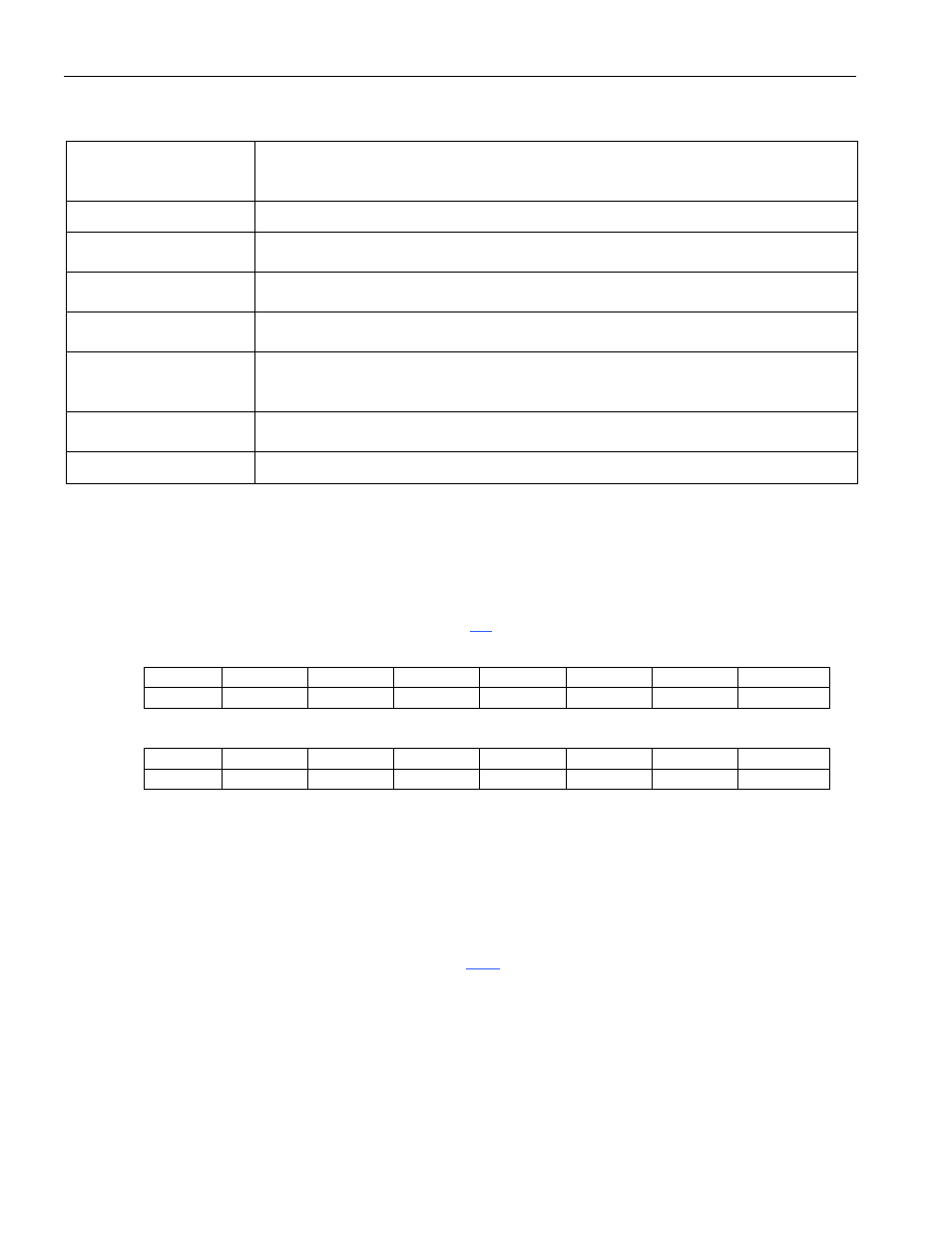

Table 7-D. Transmit Bit-Synchronous HDLC Functions

Zero Stuffing

Only used between opening and closing flags. Is disabled in between a closing flag

and an opening flag and for sending aborts and/or interfill data. Disabled if the

channel is set to the transparent mode.

Interfill Selection

Can be either 7Eh or FFh.

Flag Generation

A programmable number of flags (1 to 16) can be set between packets. Disabled if

the channel is set to the transparent mode.

CRC Generation

Can be either CRC-16 or CRC-32 or none. Disabled if the channel is set to

transparent mode.

Invert Data

All data (including the flags and FCS) is inverted after processing. Also available in

the transparent mode.

Bit Flip

The LSB (normal mode) of the byte from the FIFO becomes the first bit sent or the

MSB (telecom mode) becomes the first bit sent. Also available in the transparent

mode.

Transparent Mode

If enabled, flag generation, zero stuffing, and FCS generation is disabled.

Passes bytes from the PCI Bus to Layer 1 on octet (byte) boundaries.

Invert FCS

When enabled, it inverts all of the bits in the FCS (useful for HDLC testing).

7.3 Bit-Synchronous HDLC Register Description

Register Name:

RH[n]CR, where n= 0 to 39 (one for each port)

Register Description:

Receive HDLC Port [n] Control Register

Register Address:

See the Register Map in Section

4.5

.

Bit

# 7 6 5 4 3 2 1 0

Name RABTD

RCS RBF RID RCRC1

RCRC0

ROLD

RTRANS

Default

0 0 0 0 0 0 0 0

Bit

# 15 14 13 12 11 10 9 8

Name

reserved reserved reserved reserved reserved reserved RPEN

RZDD

Default

0 0 0 0 0 0 0 0

Note:

Bits that are underlined are read-only; all other bits are read-write.

Bit 0/Receive Transparent Enable (RTRANS). When this bit is set low, the HDLC controller performs flag

delineation, zero destuffing, abort detection, octet length checking (if enabled via ROLD), and FCS checking (if

enabled via RCRC0/1). When this bit is set high, the HDLC controller does not perform flag delineation, zero

destuffing, and abort detection, octet length checking, or FCS checking. When in transparent mode, the device

must not be configured to write done-queue descriptors only at the end of a packet if it is desired that done-queue

descriptors be written; there is not an end of packet on the receive side in transparent mode by definition. For more

information about done-queue configuration, see Section

9.3.5

: dword 1, Bit 1/Done Queue Select (DQS). Please

note that an end of packet does not occur on the receive side while in transparent mode.

0 = transparent mode disabled

1 = transparent mode enabled