Table 12-a. instruction codes – Rainbow Electronics DS3131 User Manual

Page 142

DS3131

142 of 174

If the local bus is used as 16-bit bus, then the LBW control bit must be set to 0. In 16-bit accesses, the

host can either perform a 16-bit access or an 8-bit access by asserting the appropriate PCBE signals (see

Table 11-C

). For 16-bit access, the host enables the combination of either PCBE0/PCBE1 or

PCBE2/PCBE3 and the local bus block maps the word from/to the PCI bus to/from the LD[15:0]

signals. For 8-bit access in the 16-bit bus mode, the host must assert just one of the PCBE0 to PCBE3

signals. If the host asserts a combination of PCBE signals not supported by the local bus, the local bus

rejects the access and the PCI block returns a target abort to the host. See Section

10

for details on a

target abort. Section

11.3

contains a number of timing examples for the local bus.

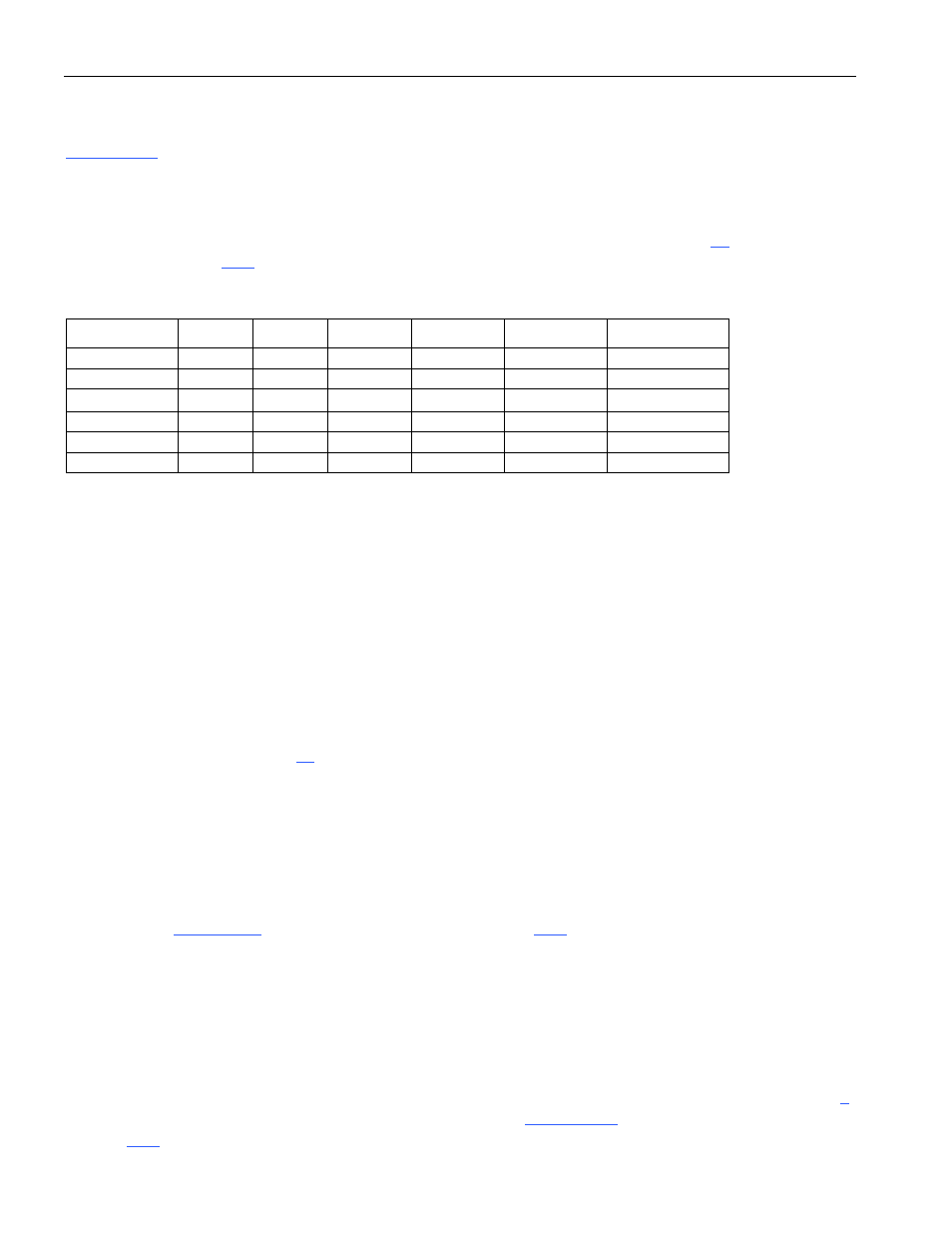

Table 11-C. Local Bus 16-Bit Width Address, LD,

LBHE

LBHE

LBHE

LBHE Setting

PCBE

PCBE

PCBE

PCBE [3:0]

8/16 A1 A0 LD[15:8]

LD[7:0]

LBHE

LBHE

LBHE

LBHE

1110 8 0 0 Active 1

1101 8 0 1

Active

0

1100

16 0 0 Active

Active

0

1011 8 1 0 Active 1

0111 8 1 1

Active

0

0011 16 1 0 Active

Active

0

Note 1:

All other possible states for

PCBE cause the device to return a target abort to the host.

Note 2:

The 16-bit data picked from the PCI bus is routed/sampled to/from the LD[7:0] and LD[15:8] signal lines as shown.

Note 3:

If no

PCBE signals are asserted during an access, a target abort is not returned and no transaction occurs on the local bus.

Bridge Mode Bus Arbitration

In bridge mode, the local bus has the ability to arbitrate for bus access. In order for this feature to

operate, the host must access the PCI bridge mode control register (LBBMC) and enable it through the

LARBE control bit (the default is bus arbitration disabled). If bus arbitration is enabled, then, before a

bus transaction can occur, the local bus first requests bus access by asserting the LHOLD (LBR) signal

and then waits for the bus to be granted from the local bus arbiter by sensing that the LHLDA (LBG) has

been asserted. If the host on the PCI bus attempts a local bus access when the local bus is not granted by

the local bus master (LBGACK is deasserted), the local bus block immediately informs the host by

issuing a PCI target retry that the local bus is busy and cannot be accessed at that time (in other words,

come back later). See Section

10

for details about the PCI target retry. When this happens, the local bus

block does not attempt the bus access and keeps the LA, LD, LBHE, LWR (LR/W), and LRD (LDS)

signals three-stated.

If the host attempts a local bus access when the bus is busy, the local bus block requests bus access, and,

after it has been granted, it seizes the bus for the time programmed into the local bus arbitration timer

(LAT0 to LAT3 in the LBBMC register), which can be from 32 to 1,048,576 clocks. As long as the local

bus has been granted and the arbitration timer has at least 16 clocks left, the host is allowed to access the

local bus. See

Figure 11-4

and the timing examples in Section

11.3

for more details.

Bridge Mode Bus Transaction Timing

When the local bus is operated in PCI bridge mode, the bus transaction time can be determined either

from an external ready signal (LRDY) or from the PCI bridge mode control register (LBBMC), which

allows a bus transaction time of 1 to 11 LCLK cycles. If the total access time to the local bus exceeds 16

PCLK cycles, the PCI access times out and a PCI target retry is sent to the host. This only occurs when

LRDY has not been detected within 9 clocks. If this happens, the local bus error (LBE) status bit in the

status master (SM) register is set. Additional details about the LBE status bit can be found in Section

5

.

More details about transaction timing can be found in

Figure 10-4

and the timing examples in

Section

11.3

.