Rainbow Electronics DS3131 User Manual

Page 73

DS3131

73 of 174

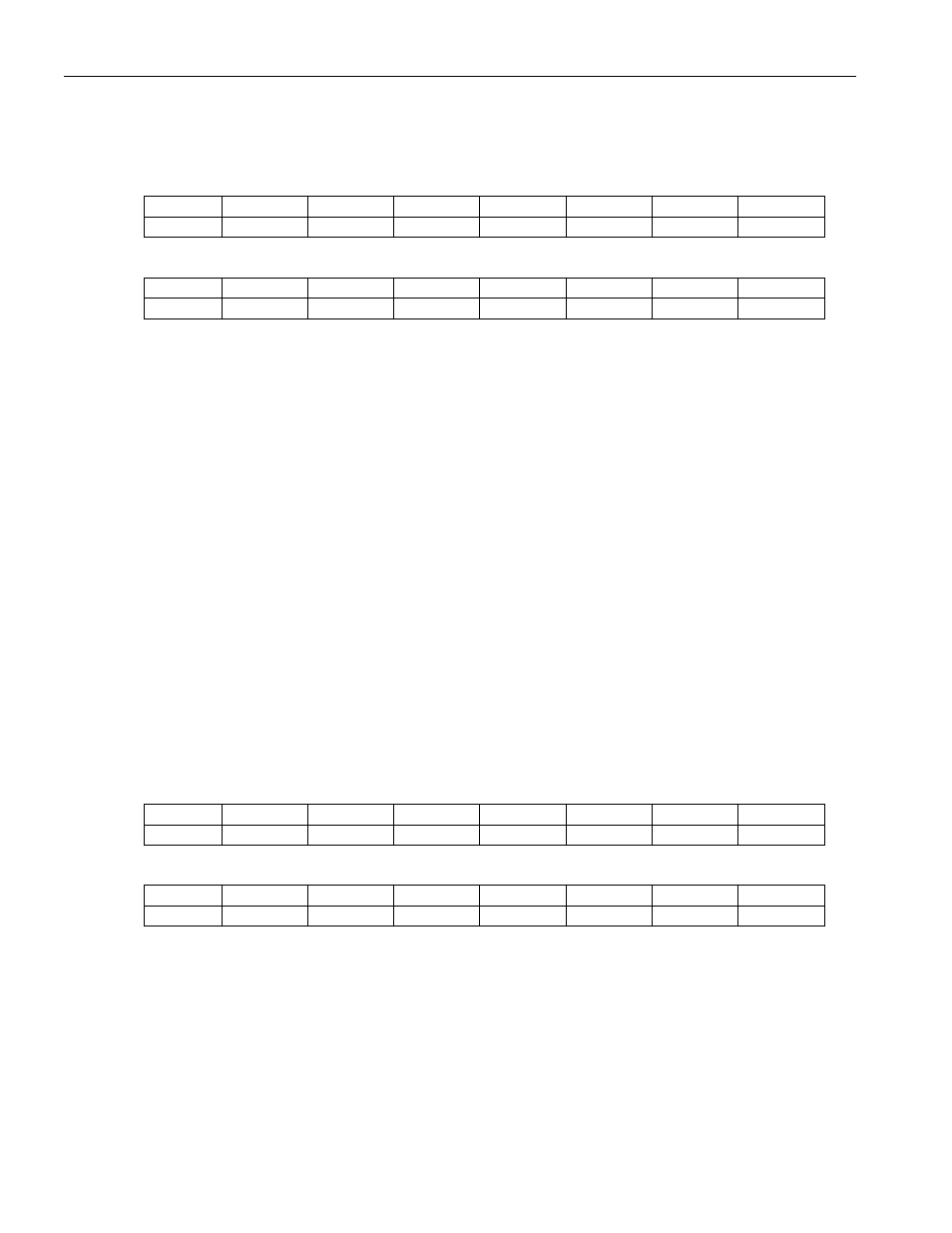

Register Name:

TFLWMIS

Register Description:

Transmit FIFO Low-Watermark Indirect Select

Register Address:

09A0h

Bit

# 7 6 5 4 3 2 1 0

Name reserved

reserved HCID5 HCID4 HCID3 HCID2 HCID1 HCID0

Default

0 0 0 0 0 0 0 0

Bit

# 15 14 13 12 11 10 9 8

Name

IAB

IARW reserved reserved reserved reserved reserved reserved

Default

0 0 0 0 0 0 0 0

Note:

Bits that are underlined are read-only, all other bits are read-write.

Bits 0 to 5/HDLC Channel ID (HCID0 to HCID5)

000000 (00h) = HDLC channel number 1

100111 (27h) = HDLC channel number 40

Bit 14/Indirect Access Read/Write (IARW). When the host wishes to read data from the internal transmit low-

watermark RAM, this bit should be written to 1 by the host. This causes the device to begin obtaining the data

from the channel location indicated by the HCID bits. During the read access, the IAB bit is set to 1. Once the data

is ready to be read from the TFLWM register, the IAB bit is set to 0. When the host wishes to write data to the

internal transmit low-watermark RAM, this bit should be written to 0 by the host. This causes the device to take

the data that is currently present in the TFLWM register and write it to the channel location indicated by the HCID

bits. When the device has completed the write, the IAB is set to 0.

Bit 15/Indirect Access Busy (IAB). When an indirect read or write access is in progress, this read-only bit is set

to 1. During a read operation, this bit is set to 1 until the data is ready to be read. It is set to 0 when the data is

ready to be read. During a write operation, this bit is set to 1 while the write is taking place. It is set to 0 once the

write operation has completed.

Register Name:

TFLWM

Register Description:

Transmit FIFO Low Watermark

Register Address:

09A4h

Bit

# 7 6 5 4 3 2 1 0

Name

TLWM7 TLWM6 TLWM5 TLWM4 TLWM3 TLWM2 TLWM1 TLWM0

Default

Bit

# 15 14 13 12 11 10 9 8

Name

reserved reserved reserved reserved reserved reserved reserved TLWM8

Default

Note:

Bits that are underlined are read-only; all other bits are read-write.

Bits 0 to 8/Low Watermark (TLWM0 to TLWM8). These nine bits indicate the setting of the transmit low

watermark. The low watermark setting is the number of blocks left in the transmit FIFO before the DMA gets

more data from the PCI bus. The low-watermark setting must be between (inclusive) one block and two less than

the number of blocks in the link-list chain for the particular channel involved. For example, if five blocks are

linked together, the low watermark can be set to 1, 2, or 3.

000000000 (000h) = invalid setting

000000001 (001h) = low watermark is 1 block

000000010 (002h) = low watermark is 2 blocks

111111111 (1FFh) = low watermark is 511 blocks