Fifo, General description and example, Eneral – Rainbow Electronics DS3131 User Manual

Page 65: Escription and, Xample, Receive high watermark, 1 general description and example, Table 8-a. fifo priority algorithm select

DS3131

65 of 174

8. FIFO

8.1 General Description and Example

The BoSS contains one 8kB FIFO for the receive path and another 8kB FIFO for the transmit path. Both

of these FIFOs are organized into blocks. Since a block is defined as 4 dwords (16 Bytes), each FIFO is

made up of 512 blocks.

Figure 8-1

shows an FIFO example.

The FIFO contains a state machine that is constantly polling the 40 ports to determine if any data is ready

for transfer to/from the FIFO from/to the HDLC engines. The 40 ports are priority decoded with Port 0

getting the highest priority and Port 39 getting the lowest priority. Therefore, all of the enabled HDLC

channels on the lower numbered ports are serviced before the higher numbered ports. As long as the

maximum throughput rate of 132Mbps is not exceeded, the DS3131 ensures that there is enough

bandwidth in this transfer to prevent any data loss between the HDLC engines and the FIFO.

The FIFO also controls which HDLC channel the DMA should service to read data out of the FIFO on

the receive side and to write data into the FIFO on the transmit side. Which channel gets the highest

priority from the FIFO is configurable through some control bits in the Master Configuration (MC)

register (

Section 5.2

). There are two control bits for the receive side (RFPC0 and RFPC1) and two

control bits for the transmit side (TFPC0 and TFPC1) that will determine the priority algorithm as shown

in

Table 8-A

. When an HDLC channel is priority decoded, the lower the number of the HDLC channel,

generally the higher the priority. Options 3 and 4 in

Table 8-A

are exceptions to this rule since they are

priority decoded in reverse order; the round robin decodes in options 3 and 4 are standard with respect to

lower channel numbers receiving higher priority than subsequent channels.

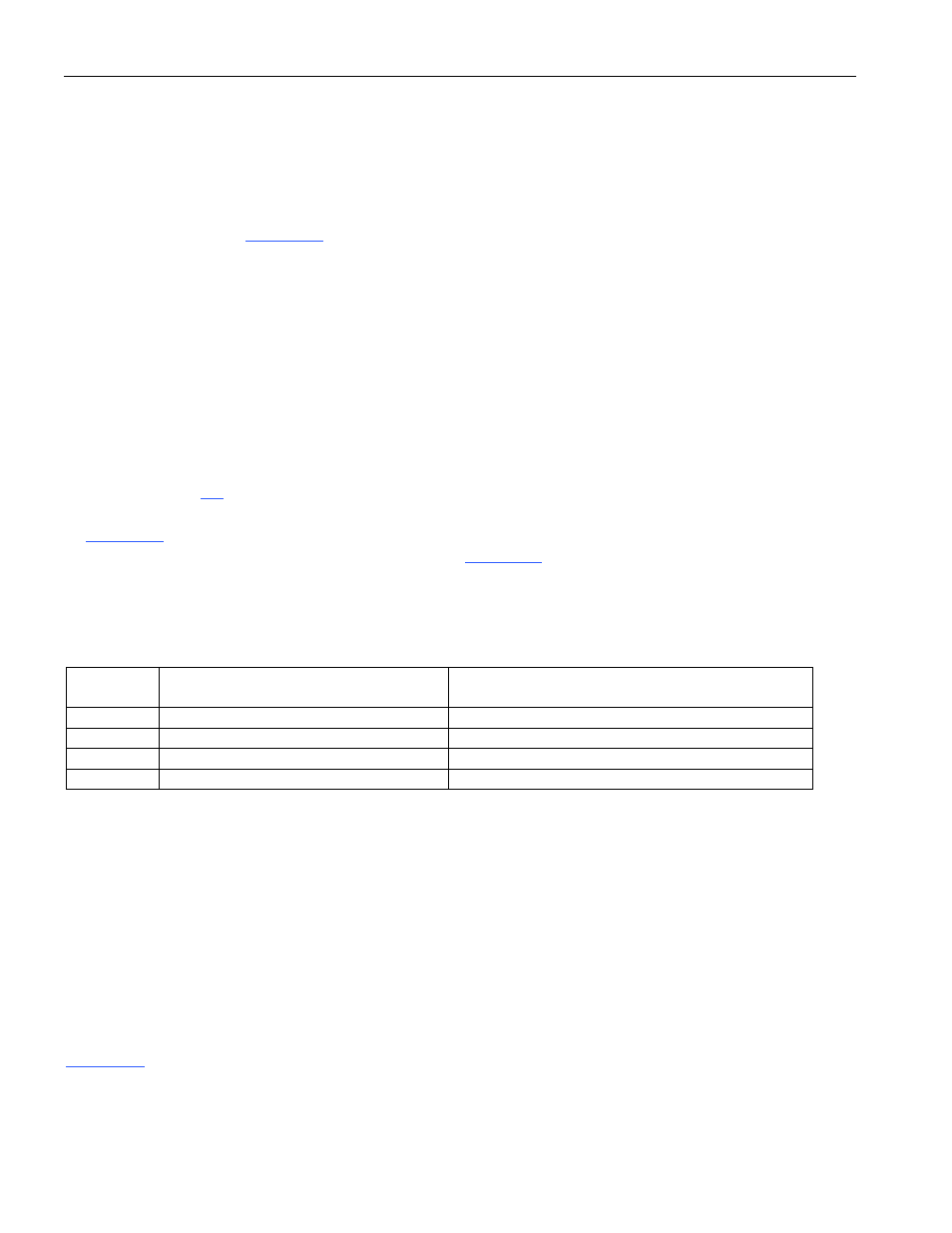

Table 8-A. FIFO Priority Algorithm Select

OPTION

HDLC CHANNELS THAT ARE

PRIORITY DECODED

HDLC CHANNELS THAT ARE SERVICED

ROUND ROBIN

1

None

Decode 1 up to 40

2

Decode 1 to 2

Then 3 up to 40

3

Decode 4, 3, 2, then 1

Then 5 up to 40

4

Decode 16, 15, 14, . . . then 1

Then 17 up to 40

To maintain maximum flexibility for channel reconfiguration, each block within the FIFO can be

assigned to any of the 40 HDLC channels. Also, blocks are link-listed together to form a chain whereby

each block points to the next block in the chain. The minimum size of the link-listed chain is 4 blocks

(64 Bytes) and the maximum is the full size of the FIFO, which is 512 blocks.

To assign a set of blocks to a particular HDLC channel, the host must configure the starting block pointer

and the block pointer RAM. The starting block pointer assigns a particular HDLC channel to a set of

link-listed blocks by pointing to one of the blocks within the chain (it does not matter which block in the

chain is pointed to). The block pointer RAM must be configured for each block that is being used within

the FIFO. The block pointer RAM indicates the next block in the link-listed chain.

Figure 8-1

shows an example of how to configure the starting block pointer and the block pointer RAM.

In this example, only three HDLC channels are being used (channels 2, 6, and 16). The device knows

that channel 2 has been assigned to the eight link-listed blocks of 112, 118, 119, 120, 121, 122, 125, and

126 because a block pointer of 125 has been programmed into the channel 2 position of the starting