Table 2-b. initialization steps, Table 2-a. restrictions – Rainbow Electronics DS3131 User Manual

Page 12

DS3131

12 of 174

Restrictions

In creating the overall system architecture, the user must balance the port, throughput, and HDLC

channel restrictions of the DS3131.

Table 2-A

lists all of the upper-bound maximum restrictions.

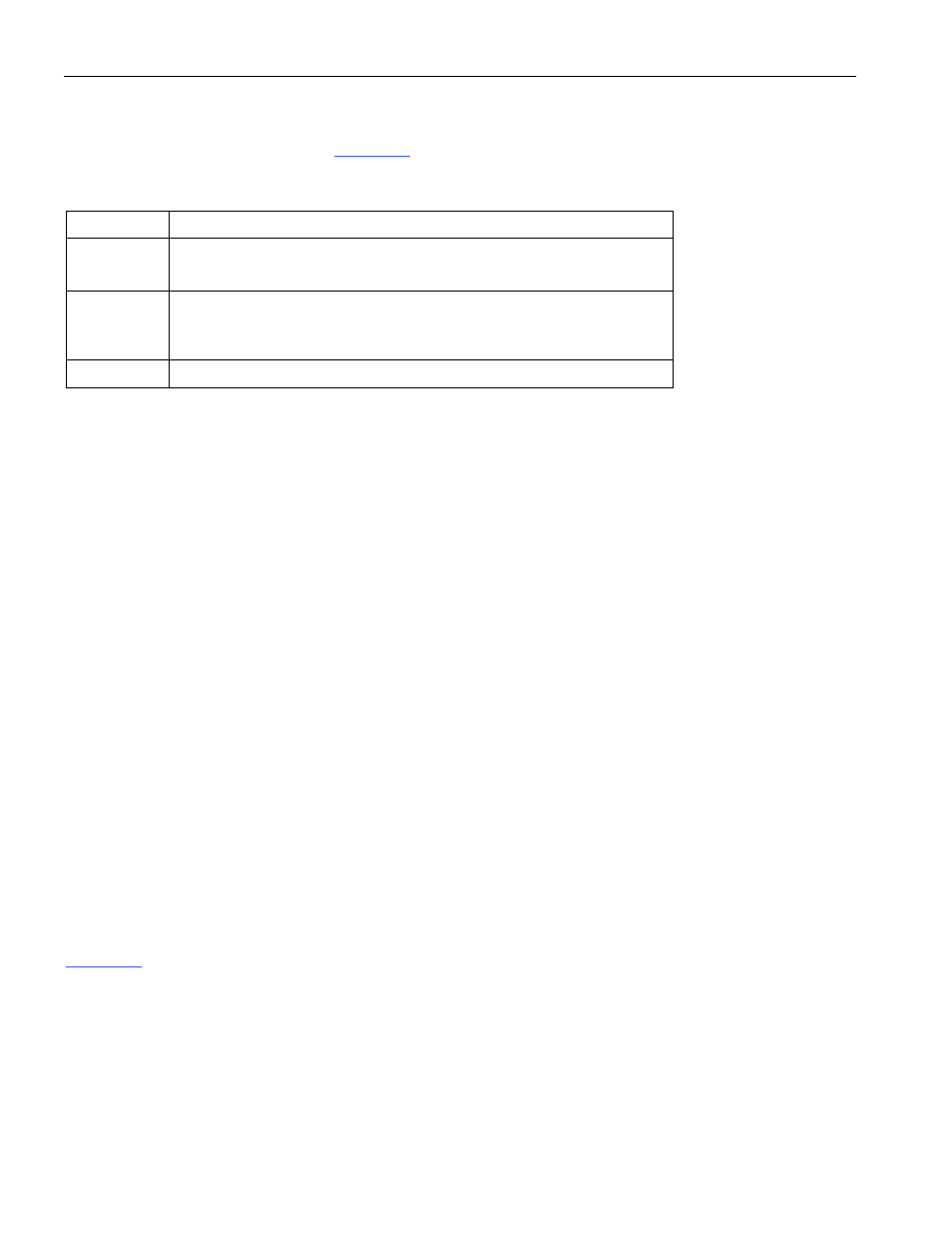

Table 2-A. Restrictions

ITEM RESTRICTION

Maximum of 40 physical ports

Port

Maximum data rate of 52Mbps

Maximum receive: 132Mbps (Refer to Application Note 358: DS3134

PCI Bus Utilization.)

Throughput

Maximum transmit: 132Mbps

HDLC

Maximum of 40 channels

Internal Device Configuration Registers

All internal device configuration registers (with the exception of the PCI configuration registers, which

are 32-bit registers) are 16 bits wide and are not byte addressable. When the host on the PCI bus accesses

these registers, the particular combination of byte enables (i.e., PCBE signals) is not important, but at

least one of the byte enables must be asserted for a transaction to occur. All registers are read/write,

unless otherwise noted. Reserved bits should not be modified to allow for future upgrades to the device.

These bits should be treated as having no meaning and could be either 0 or 1 when read.

Initialization

On a system reset (which can be invoked by either hardware action through the PRST signal or software

action through the RST control bit in the master reset and ID register), all of the internal device

configuration registers are set to 0 (0000h). The local bus bridge mode control register (LBBMC) is not

affected by a software-invoked system reset; it is forced to all zeros only by a hardware reset. The

internal registers that are accessed indirectly (these are listed as “indirect registers” in the data sheet and

consist of the port DS0 configuration registers in the Layer 1 block, the DMA configuration RAMs, and

the FIFO registers) are not affected by a system reset, so they must be configured on power-up by the

host to a proper state.

By design, the DS3131 BoSS does not take control of the PCI bus upon power-up. All physical ports

start up by sending all ones (not the HDLC idle code), so the BoSS is idle upon power-up. Please note,

however, that the BoSS uses internal RAM to periodically store and retrieve the states of the internal

state machines. Because there are many such complex state machines and interworking functional blocks

inside the BoSS, all internal registers must be initialized to a known state before any data packets can be

transmitted and received.

Table 2-B

lists the steps required to initialize the DS3131. It is imperative that they are followed exactly

in the order presented, or exactly as implemented in Dallas Semiconductor DS3131 driver code.