Rainbow Electronics DS3131 User Manual

Page 63

DS3131

63 of 174

Register Name:

RHPL

Register Description:

Receive HDLC Maximum Packet Length

Register Address:

03A0h

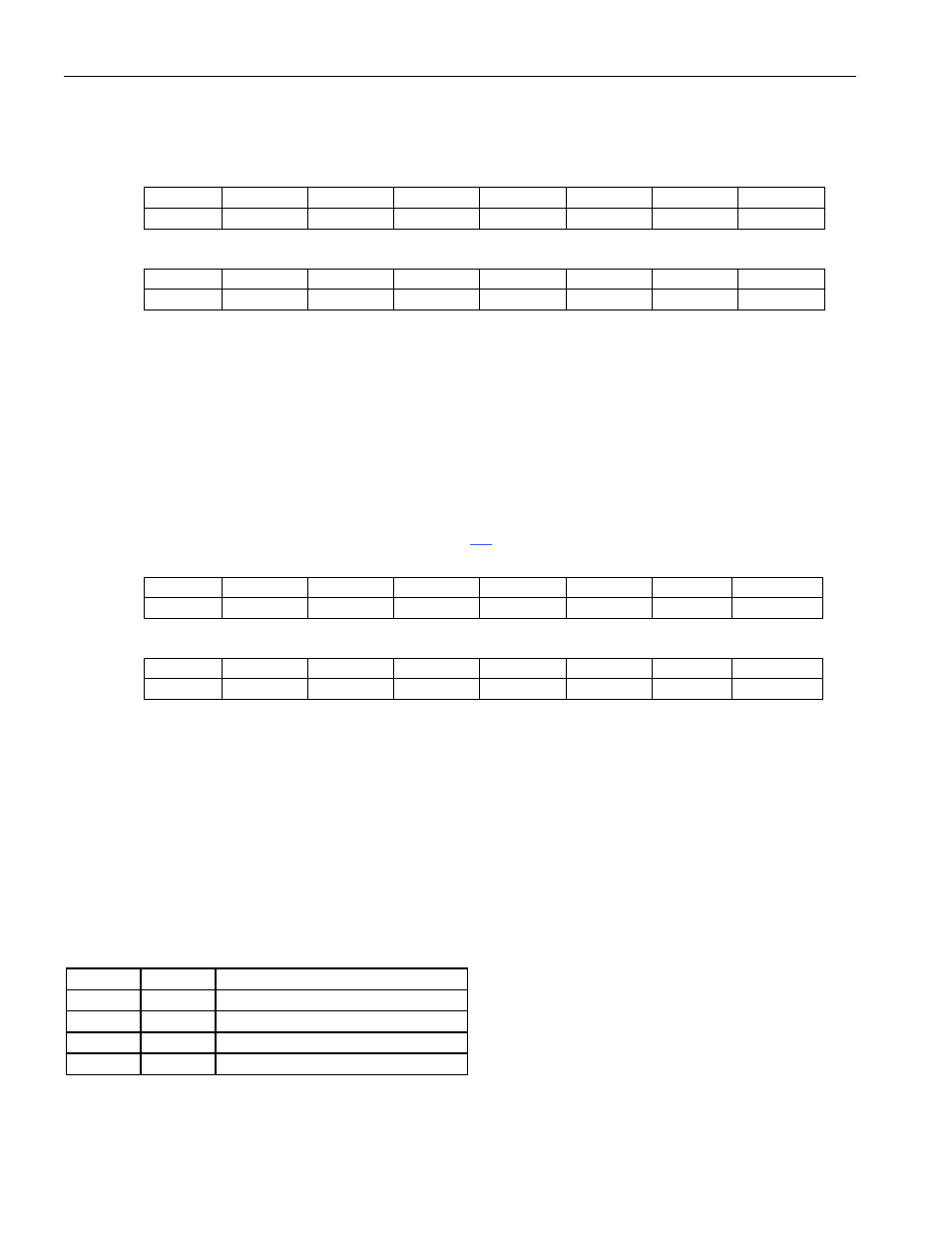

Bit

# 7 6 5 4 3 2 1 0

Name

RHPL7 RHPL6 RHPL5 RHPL4 RHPL3 RHPL2 RHPL1 RHPL0

Default

0 0 0 0 0 0 0 0

Bit

# 15 14 13 12 11 10 9 8

Name

RHPL15 RHPL14 RHPL13 RHPL12 RHPL11 RHPL10 RHPL9 RHPL8

Default

0 0 0 0 0 0 0 0

Note:

Bits that are underlined are read-only; all other bits are read-write.

Bits 0 to 15/Receive Bit-Synchronous HDLC Maximum Packet Length (RHPL0 to RHPL15). If the receive

octet length-detection enable (ROLD) bit is set to 1, the HDLC controller checks the number of received octets in

a packet to see if they exceed the count in this register. If the length is exceeded, the packet is aborted and the

remainder is discarded. The definition of “octet length” is everything between the opening and closing flags which

includes the address field, control field, information field, and FCS.

Register Name:

TH[n]CR, where n = 0 to 39 (one for each port)

Register Description:

Transmit HDLC Port [n] Control Register

Register Address:

See the Register Map in Section

4.6

.

Bit

# 7 6 5 4 3 2 1 0

Name TABTE

TCFCS TBF TID TCRC1

TCRC0

TIFS

TTRANS

Default

0 0 0 0 0 0 0 0

Bit

# 15 14 13 12 11 10 9 8

Name reserved

reserved

reserved

TZSD TFG3 TFG2 TFG1 TFG0

Default

0 0 0 0 0 0 0 0

Note: Bits that are underlined are read-only, all other bits are read-write.

Bit 0/Transmit Transparent Enable (TTRANS). When this bit is set low, the HDLC controller generates flags

and the FCS (if enabled through TCRC0/1) and performs zero stuffing. When this bit is set high, the HDLC

controller does not generate flags or the FCS and does not perform zero stuffing.

0 = transparent mode disabled

1 = transparent mode enabled

Bit 1/Transmit Interfill Select (TIFS)

0 = the interfill byte is 7Eh (01111110)

1 = the interfill byte is FFh (11111111)

Bits 2, 3/Transmit CRC Selection (TCRC0/TCRC1). These bits are ignored if the HDLC channel is set to

transparent mode (TTRANS = 1).

TCRC1 TCRC0

ACTION

0

0

No CRC is generated

0

1

16-bit CRC (CCITT/ITU Q.921)

1 0

32-bit

CRC

1 1

Illegal

state