Hdlc, General description, Hdlc operation – Rainbow Electronics DS3131 User Manual

Page 59: Eneral, Escription, Hdlc o, Peration, Ynchronous, Egister

DS3131

59 of 174

7. HDLC

7.1 General Description

Each port on the DS3131 has a dedicated bit-synchronous HDLC controller that can operate up to

52Mbps. See

Figure 2-2

and

Figure 6-1

. HDLC channel numbers are assigned as shown below in

Table 7-A

.

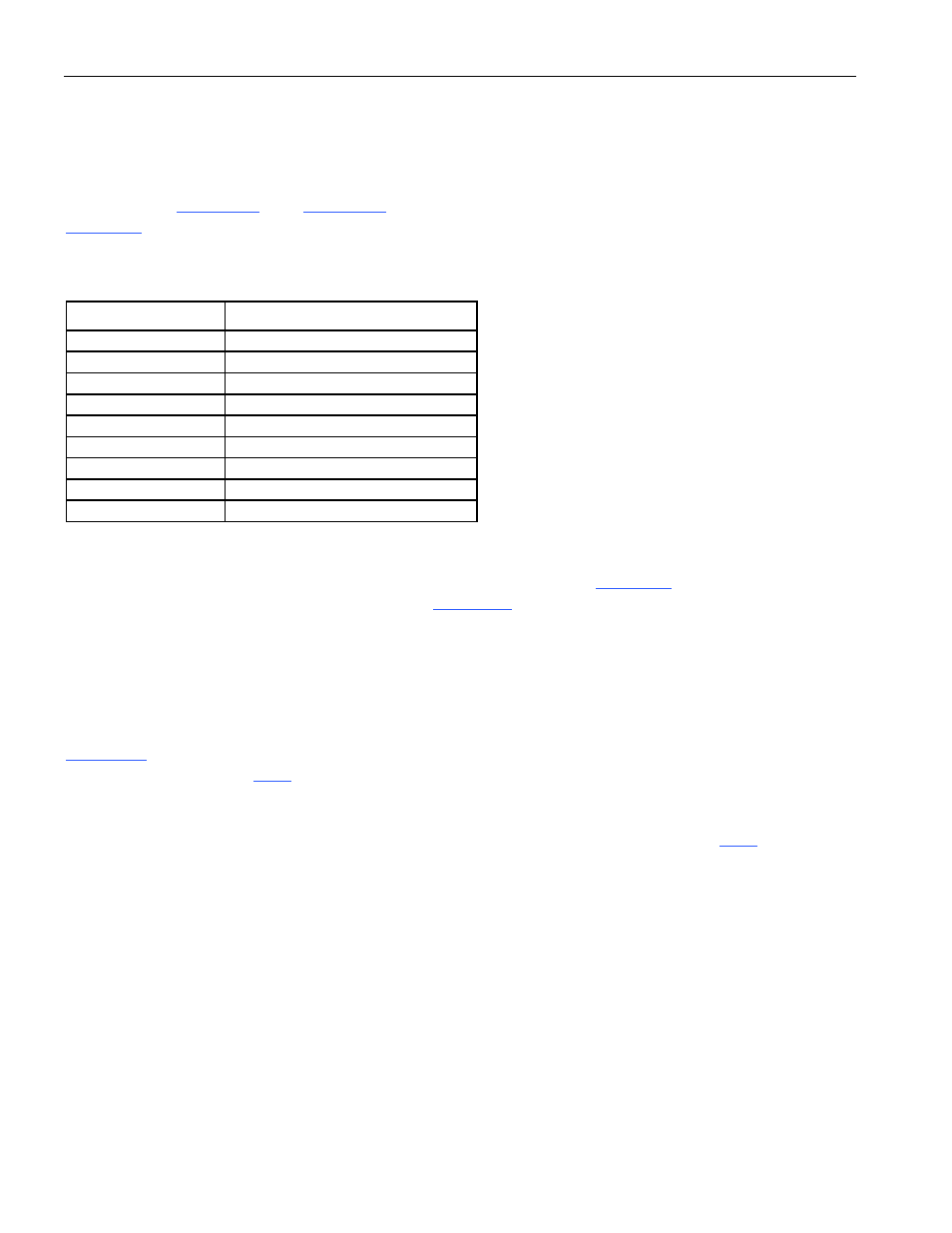

Table 7-A. HDLC Channel Assignment

PORT NUMBER

HDLC CHANNEL NUMBER

0 1

1 2

2 3

3 4

4 5

. . .

. . .

37 38

38 39

39 40

7.2 HDLC Operation

The HDLC controllers can handle all normal real-time tasks required.

Table 7-C

lists all of the functions

supported by the receive HDLC controller and

Table 7-D

lists all functions supported by the transmit

HDLC controller. Each of the 40 HDLC channels within the BoSS are configured by the host through

the receive HDLC control register (RH[n]CR) and transmit HDLC control register (TH[n]CR). There is a

separate RHCR and THCR register for each HDLC channel; the host can access the respective RH[n]CR

and TH[n]CR registers directly.

On the receive side, when the HDLC block is processing a packet, one of the outcomes shown in

Table 7-B

occurs. For each packet, one of these outcomes is reported in the receive done-queue

9.2.4

for details.) On the transmit side, when the HDLC block is processing a

packet, an error in the PCI block (parity or target abort) or transmit FIFO underflow causes the HDLC

block to send an abort sequence (eight 1s in a row) followed continuously by the selected interfill (either

7Eh or FFh) until the HDLC channel is reset by the transmit DMA block (Section

9.3.1

). This same

sequence of events occurs even if the transmit HDLC channel is operating in the transparent mode. If the

FIFO is empty, the interfill byte (either 7Eh or FFh) is sent until an outgoing packet is ready for

transmission.