Local bus, General description, Eneral – Rainbow Electronics DS3131 User Manual

Page 138: Escription, Pci bridge mode, 1 general description

DS3131

138 of 174

11. LOCAL

BUS

11.1 General Description

The DS3131’s local bus can be either enabled or disabled. When it is disabled, the device uses the local

bus signals to connect to bit-synchronous HDLC controllers on ports 28 to 39 (HDLC channels 29 to

40). The local bus is enabled and disabled through a hardware control signal called LBPXS. The local

bus is enabled when LBPXS is left open-circuited (or connected high). It is disabled when LBPXS is

connected low. See Section

2

for some diagrams detailing the possible configurations.

The local bus can operate in two modes, either as a PCI bridge (master mode) or as a configuration bus

(slave mode). This selection is made in hardware by connecting the LMS pin high or low. Figure 11–1,

Figure 11–2, and Figure 11–3 showcase the two modes.

Figure 11-1

shows an example of the local bus

operating in the PCI bridge mode. In this example, the host can access the control ports on the xDSL

devices through the local bus.

Figure 11-2

also shows an example of the PCI bridge mode but the local

bus arbitration is enabled, which allows a local CPU to control when the host can have access to the local

bus. To access the local bus, the host must first request the bus and then wait until it is granted.

Figure 11-3

features an example of the configuration mode. In this mode, the CPU on the local bus

configures and monitors the DS3131. The host on the PCI/custom bus cannot access the DS3131 and the

PCI/custom bus is only used to transfer HDLC packet data to and from the host.

Table 11-A

lists all the local bus pins and their applications in both operating modes. The local bus

operates only in a nonmultiplexed fashion; it is not capable of operating as a multiplexed bus. For both

operating modes, the local bus can be set up for either Intel or Motorola type buses. This selection is

made in hardware by connecting the LIM pin high or low.

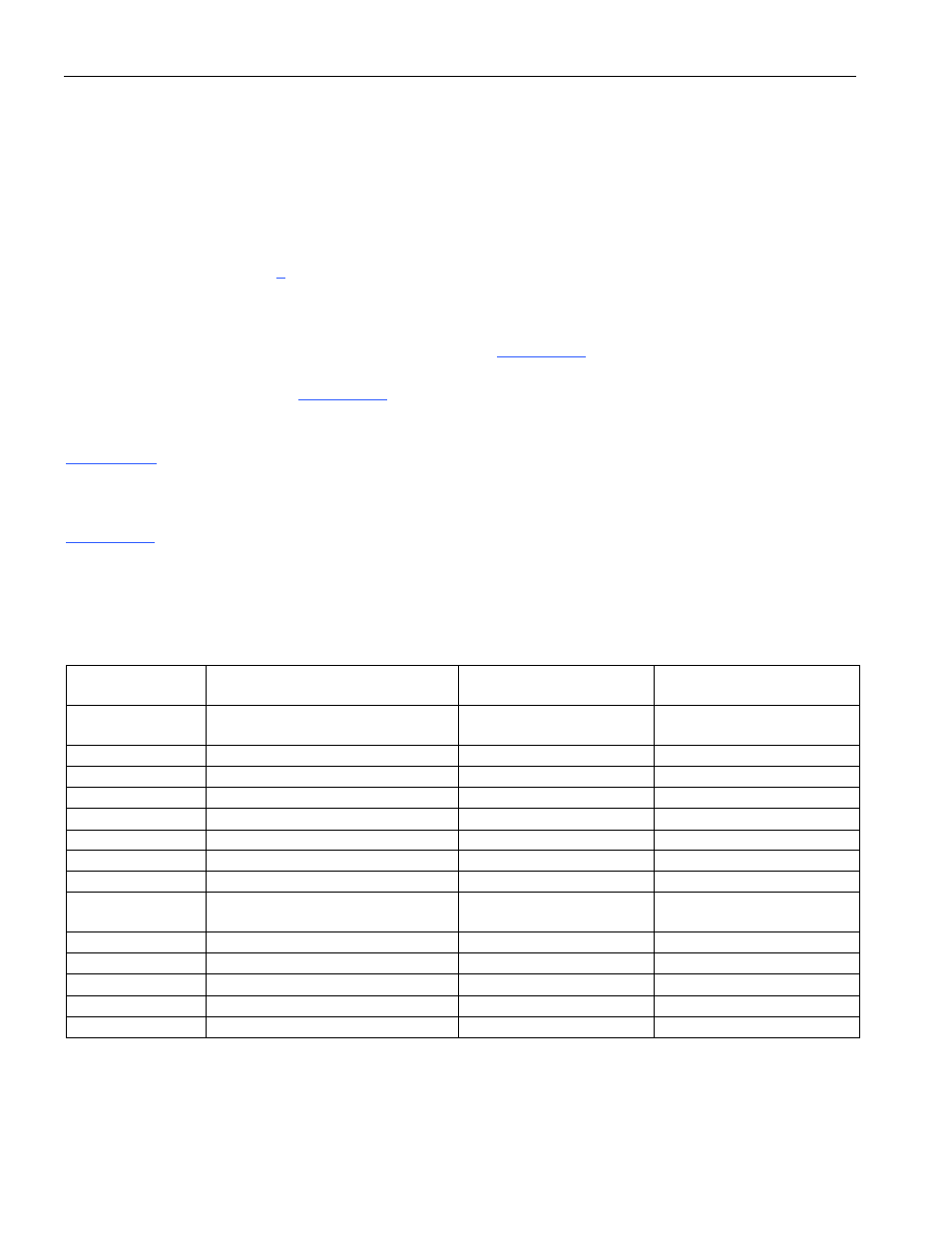

Table 11-A. Local Bus Signals (LBPXS Floating or Connected High)

SIGNAL FUNCTION

PCI BRIDGE

MODE (LMS = 0)

CONFIGURATION

MODE (LMS = 1)

LD[0:15] Data

Bus

Input on Read/Output on

Write

Input on Write/Output on

Read

LA[0:19] Address

Bus

Output

Input

LWR (LR/W)

Bus Write (Read/Write Select)

Output

Input

LRD (LDS)

Bus Read (Data Strobe)

Output

Input

LBHE

Byte High Enable

Output

Three-stated

LIM Intel/Motorola

Select

Input

Input

LINT

Interrupt Input

Output

LMS Mode

Select

Input

Input

LCLK

Bus Clock (Use of PCLK is

recommended in bridge mode.)

Output Three-stated

LRDY

Bus Ready

Input

Ignored

LCS

Chip Select

Ignored

Input

LHOLD(LBR)

Hold Request (Bus Request)

Output

Three-stated

LHLDA(LBG)

Hold Acknowledge (Bus Grant)

Input

Ignored

LBGACK

Bus Acknowledge

Output

Three-stated

Note:

Signals shown in parenthesis ( ) are active when Motorola Mode (LIM = 1) is selected.