Table e8. encoding of 32-bit address mode with “m – Intel 386 User Manual

Page 665

Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

E-28

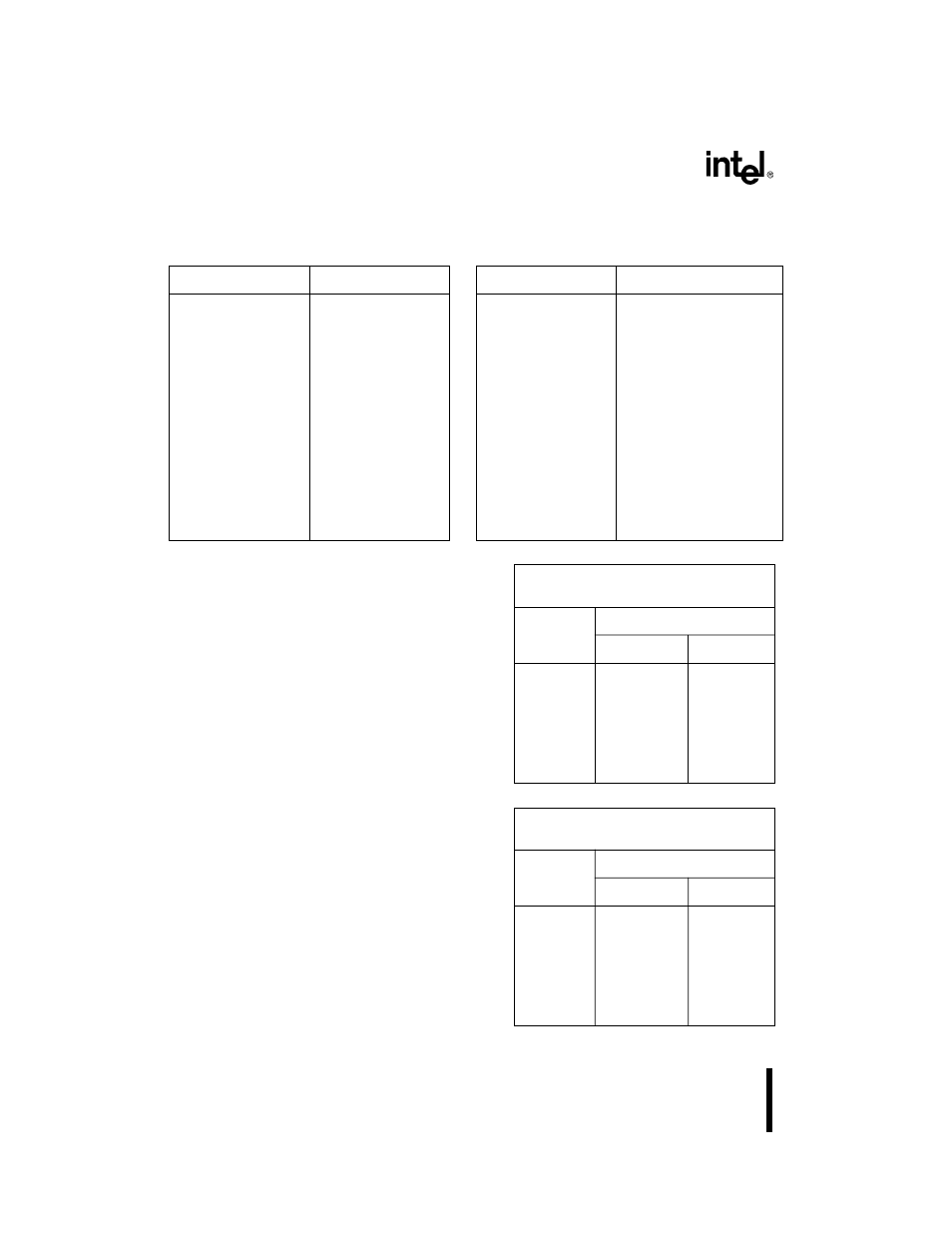

Table E-8. Encoding of 32-bit Address Mode with “mod r/m” Byte (No s-i-b Byte Present)

mod r/m

Effective Address

mod r/m

Effective Address

00 000

00 001

00 010

00 011

00 100

00 101

00 110

00 111

01 000

01 001

01 010

01 011

01 100

01 101

01 110

01 111

DS:[EAX]

DS:[ECX]

SS:[EDX]

SS:[EBX]

s-i-b is present

DS:[d32]

DS:[ESI]

DS:[EDI]

DS:[EAX + d8]

DS:[ECX + d8]

SS:[EDX + d8]

SS:[EBX + d8]

s-i-b is present

SS:[EBP + d8]

DS:[ESI + d8]

DS:[EDI + d8]

10 000

10 001

10 010

10 011

10 100

10 101

10 110

10 111

11 000

11 001

11 010

11 011

11 100

11 101

11 110

11 111

DS:[EAX + d32]

DS:[ECX + d32]

SS:[EDX + d32]

SS:[EBX + d32]

s-i-b is present

SS:[EBP + d32]

SS:[ESI + d32]

DS:[EDI + d32]

register - see tables below

register - see tables below

register - see tables below

register - see tables below

register - see tables below

register - see tables below

register - see tables below

register - see tables below

Register Specified by r/m

During 16-bit Data Operations

mod r/m

Function of w Field

(when w = 0)

(when w = 1)

11 000

11 001

11 010

11 011

11 100

11 101

11 110

11 111

AL

CL

DL

BL

AH

CH

DH

BH

AX

CX

DX

BX

SP

BP

SI

DI

Register Specified by r/m

During 32-bit Data Operations

mod r/m

Function of w Field

(when w = 0)

(when w = 1)

11 000

11 001

11 010

11 011

11 100

11 101

11 110

11 111

AL

CL

DL

BL

AH

CH

DH

BH

EAX

ECX

EDX

EBX

ESP

EBP

ESI

EDI