Table 102. tcu associated registers – Intel 386 User Manual

Page 247

Intel386™ EX EMBEDDED PROCESSOR USER’S MANUAL

10-4

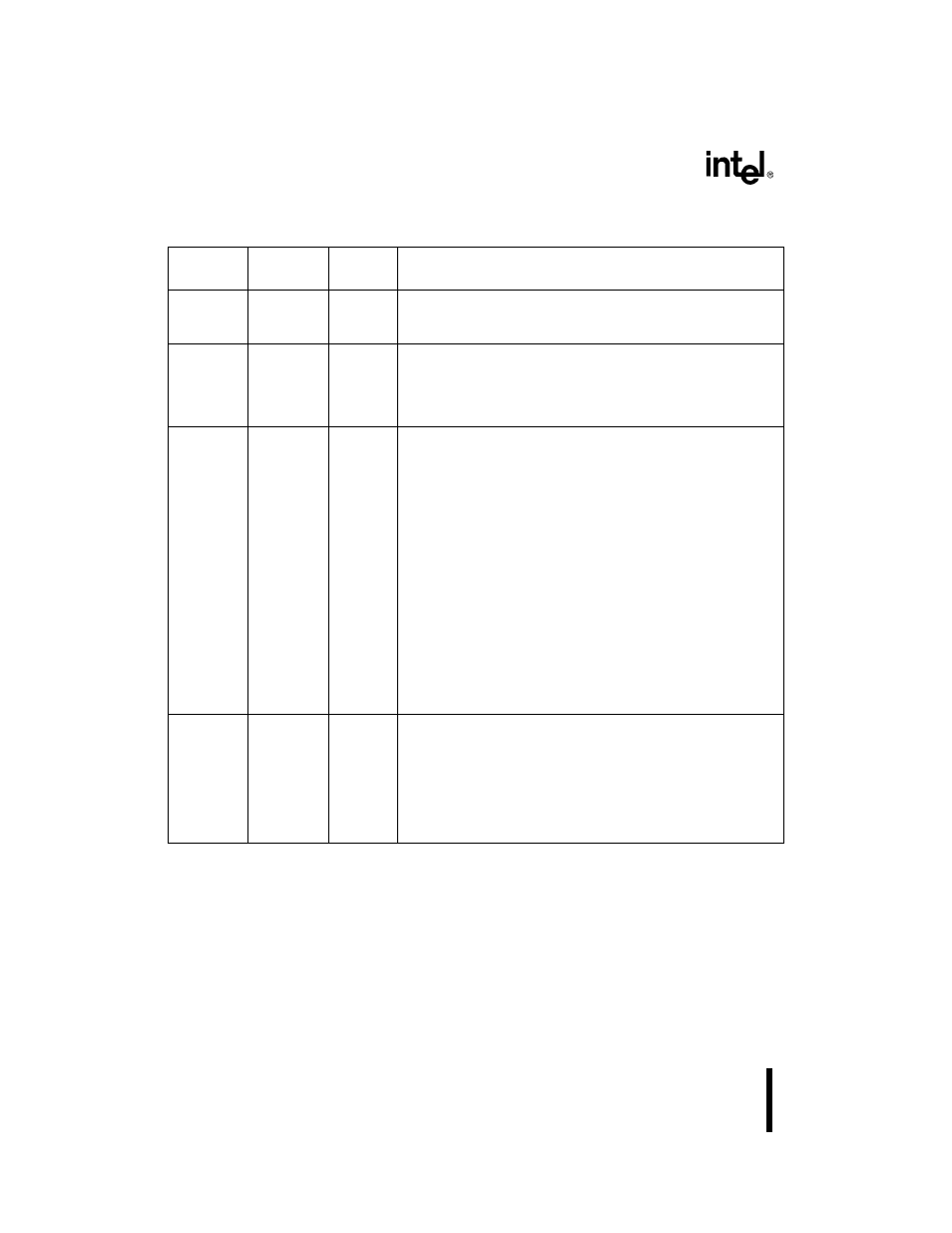

Table 10-2. TCU Associated Registers

Register

Expanded

Address

PC/AT*

Address

Function

P3CFG

PINCFG

(read/write)

0F824H

0F826H

—

Peripheral Pin Selections:

These registers determine whether a counter’s input and output

signals are connected to package pins.

TMRCFG

(read/write)

0F834H

—

Timer Configuration:

Enables the counter’s CLKIN

n input signal, selects the CLKINn

connection (PSCLK or TMRCLK

n) for each counter, and either

connects TMRGATE

n or V

CC

to each counter’s GATE

n input signal,

or sets GATE

n high or low through register bits.

TMRCON

0F043H

0043H

TMRCON has three formats: control word, counter-latch, and read-

back. When writing to TMRCON, certain bit settings determine which

format is accessed.

Control Word Format:

Programs a specific counter. Selects a counter’s operating mode and

count format. After programming a counter, you can write a count

value to the counter’s TMR

n register at any time.

Counter-latch Format:

Issues a counter-latch command to a specific counter. The counter-

latch command allows you to latch the count of a specified counter.

After issuing a counter-latch command, you can check the counter’s

count by reading the counter’s TMR

n register.

Read-back Format:

Issues a read-back command to one or more counters. The read-

back command allows you to latch the count and status of one or

more counters. After issuing the read-back command, you can check

the counter’s status by reading the counter’s TMR

n register. After

checking a counter’s status, you can read the counter’s TMR

n

register again to check its count.

TMR0

TMR1

TMR2

0F040H

0F041H

0F042H

0040H

0041H

0042H

Status Format:

Read this register after issuing a read-back command to check

counter

n’s status. Reading TMRn again accesses its read format.

Read Format:

Read this register to check counter

n’s count value.

Write Format:

Write this register at any time after initializing counter

n to change the

counter’s count value.