4 organization of peripheral registers, Table 41. peripheral register i/o address map in – Intel 386 User Manual

Page 56

4-5

SYSTEM REGISTER ORGANIZATION

The Intel386 EX processor uses slot 15 for the registers needed for integrated peripherals. Using

this slot avoids conflicts with other devices in an EISA system, since EISA systems typically do

not use slot 15.

4.4

ORGANIZATION OF PERIPHERAL REGISTERS

The registers associated with the integrated peripherals are physically located in slot 15 of the I/O

space. There are sixteen 4 Kbyte address slots in I/O space. Slot 0 refers to 0H–0FFFH; slot 15

refers to 0F000H–0FFFFH. Table 4-1 shows the address map for the peripheral registers in slot

15. Note that the I/O addresses fall in address ranges 0F000H–0F0FFH, 0F400H–0F4FFH, and

0F800H–0F8FFH; utilizing the unique sets of 256 I/O addresses in Slot 15.

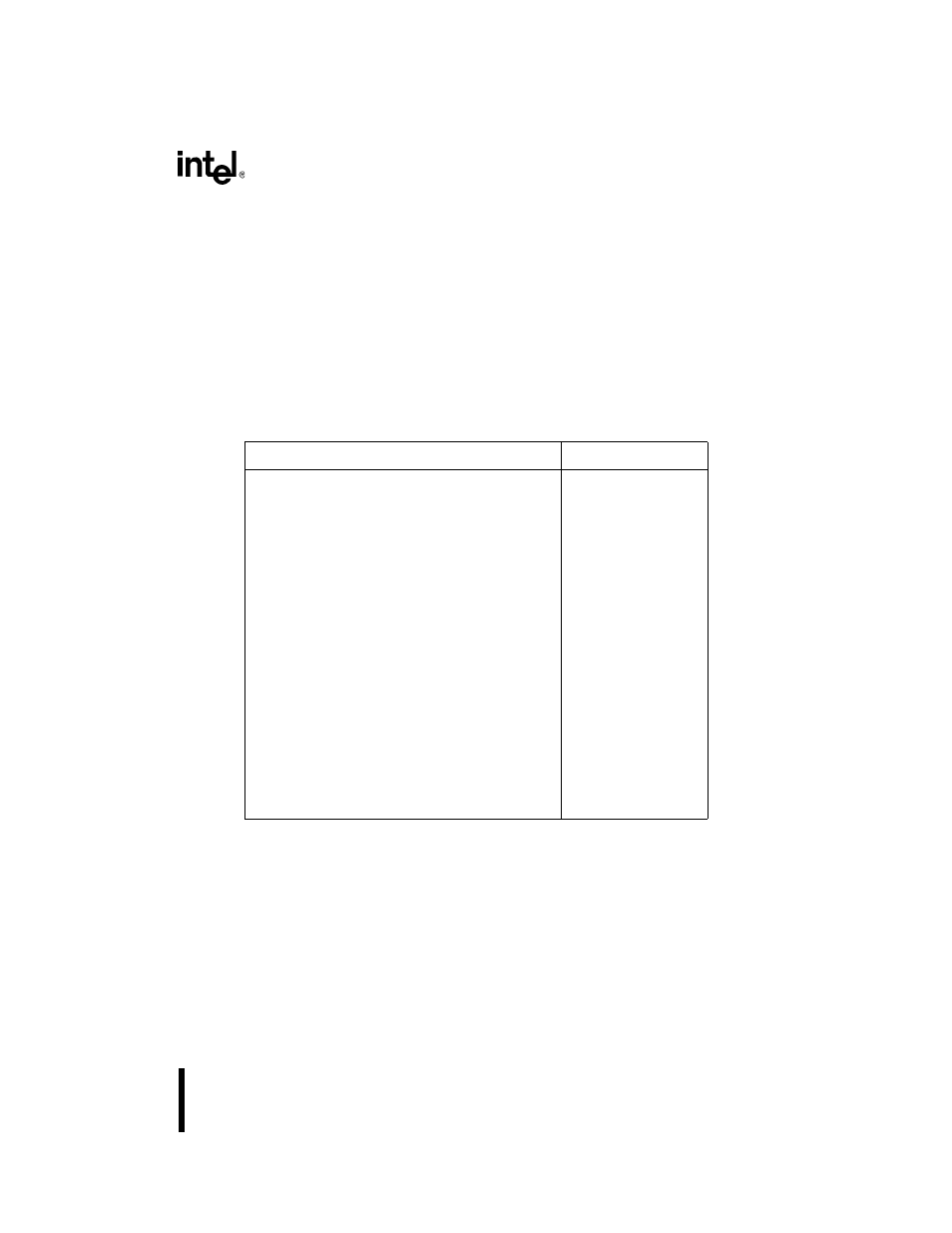

Table 4-1. Peripheral Register I/O Address Map in Slot 15

Register Description

I/O Address Range

DMA Controller 1

0F000H

–

0F01FH

Master Interrupt Controller

0F020H

–

0F03FH

Programmable Interval Timer

0F040H

–

0F05FH

DMA Page Registers

0F080H

–

0F09FH

Slave Interrupt Controller

0F0A0H

–

0F0BFH

Math Coprocessor

0F0F0H

–

0F0FFH

Chip Select Unit

0F400H

–

0F47FH

Synchronous Serial I/O Unit

0F480H

–

0F49FH

DRAM Refresh Control Unit

0F4A0H

–

0F4BFH

Watchdog Timer Unit

0F4C0H

–

0F4CFH

Asynchronous Serial I/O Channel 0 (COM1)

0F4F8H

–

0F4FFH

Clock Generation and Power Management Unit

0F800H

–

0F80FH

External/Internal Bus Interface Unit

0F810H

–

0F81FH

Chip Configuration Registers

0F820H

–

0F83FH

Parallel I/O Ports

0F860H

–

0F87FH

Asynchronous Serial I/O Channel 1 (COM2)

0F8F8H

–

0F8FFH