9 operation command word 3 (ocw3), Figure 915. operation command word 3 (ocw3) – Intel 386 User Manual

Page 226

9-27

INTERRUPT CONTROL UNIT

9.3.9

Operation Command Word 3 (OCW3)

Use OCW3 to enable the special mask mode, issue a poll command, and provide access to the

interrupt in-service and request registers (ISR, IRR).

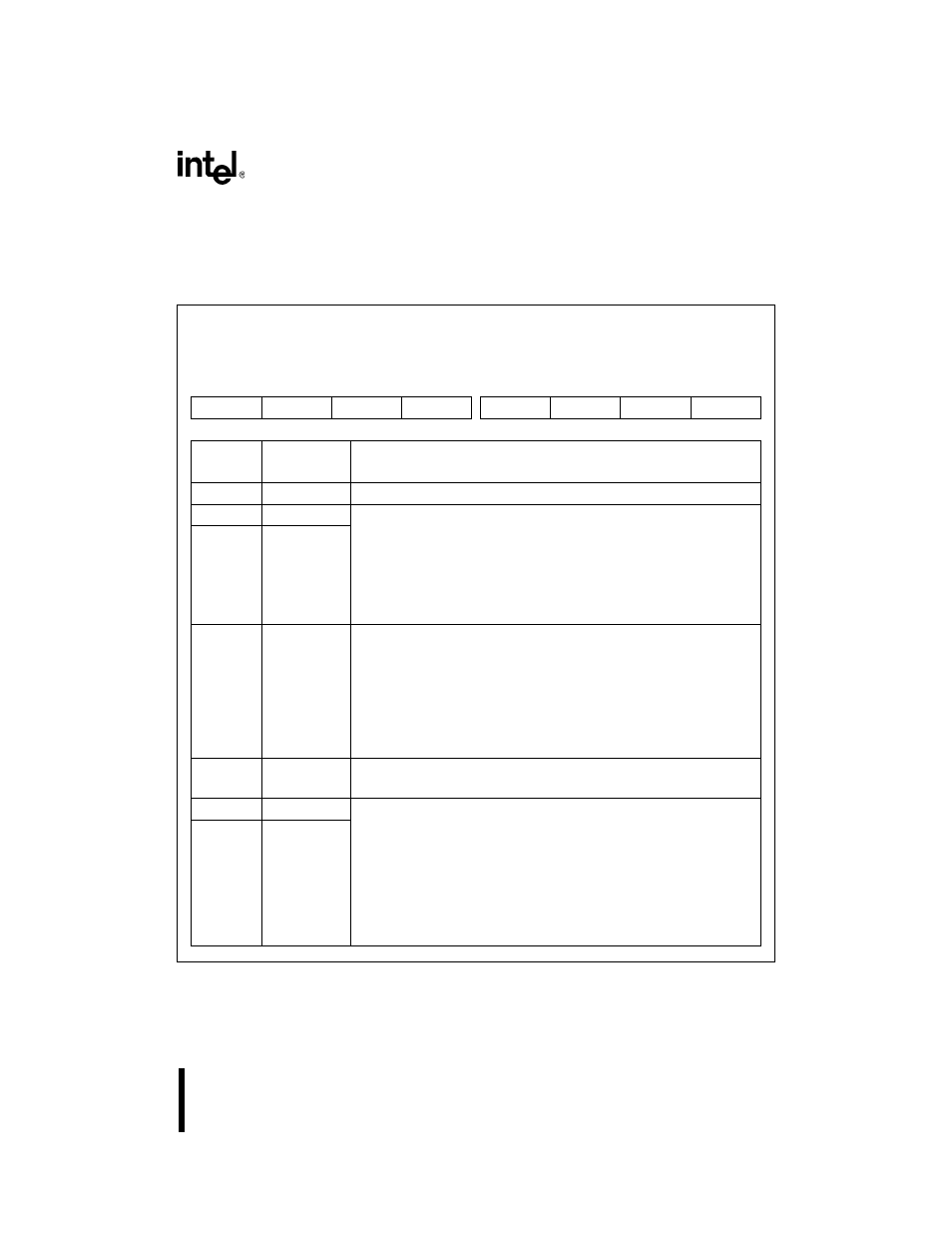

Figure 9-15. Operation Command Word 3 (OCW3)

Operation Command Word 3

OCW3 (master and slave)

(write only)

Expanded Addr:

ISA Addr:

Reset State:

master

slave

F020H

F0A0H

0020H

00A0H

XXH

XXH

7

0

0

ESMM

SMM

RSEL1

RSEL0

POLL

ENRR

RDSEL

Bit

Number

Bit

Mnemonic

Function

7

—

Clear this bit to guarantee device operation.

6

ESMM

Enable Special Mask Mode (ESMM) and Special Mask Mode (SMM):

Use these bits to enable or disable special mask mode.

ESMM

SMM

0

0

No action

0

1

No action

1

0

Disable special mask mode

1

1

Enable special mask mode

5

SMM

4–3

RSEL1:0

Register Select:

ICW1, OCW2 and OCW3 are accessed through the same addresses.

The states of RSEL1:0 determine which register is accessed. Write 01

to these bits to access OCW3.

RSEL1

RSEL0

0

0

OCW2

0

1

OCW3

1

X

ICW1

2

POLL

Poll Command:

Set this bit to issue a poll command, thus initiating the polling process.

1

ENRR

Enable Register Read Select (ENRR) and Read Register Select

(RDSEL):

These bits select which register is read during the next F020H and

F0A0H (or PC/AT address 0020H, 00A0H) read access.

ENRR

RDSEL

Register Read on Next Read Pulse

0

0

No action

0

1

No action

1

0

Interrupt Request Register

1

1

In-service Register

0

RDSEL