10 software request register (dmasrr), Figure 1227. dma software request register (dmasr – Intel 386 User Manual

Page 377

Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

12-42

12.3.10 Software Request Register (DMASRR)

Write DMASRR to issue software DMA service requests. Software requests are subject to bus

control priority arbitration with all other software and hardware requests. A software request ac-

tivates the internal channel request signal. This signal remains active until the channel completes

its buffer transfer (either by an expired byte count or an EOP# input). In the demand data-transfer

mode, a buffer transfer is suspended by deactivating the channel request signal. Because you can-

not deactivate the internal channel request signal before the end of a buffer transfer, you cannot

use software requests with demand data-transfer mode.

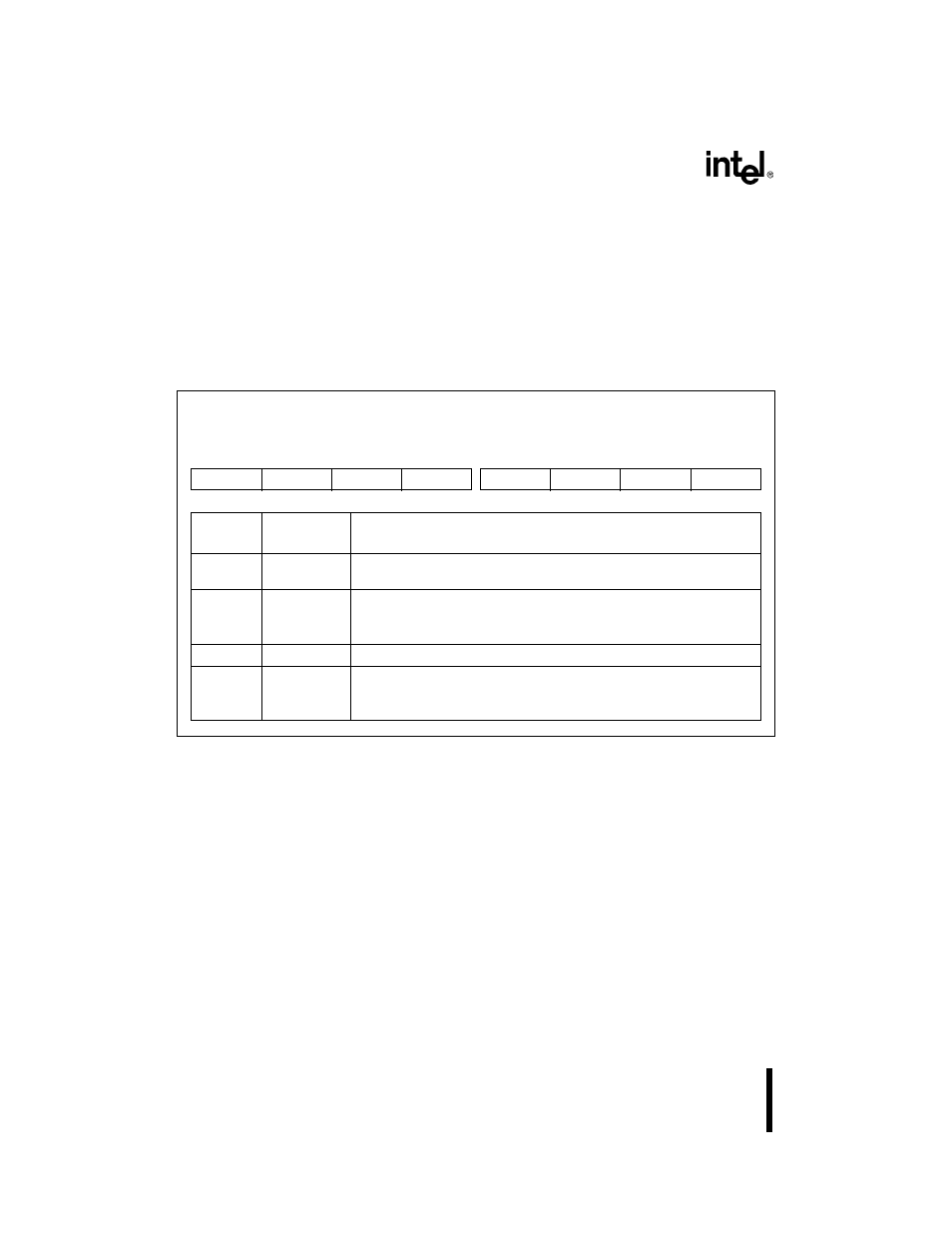

Figure 12-27. DMA Software Request Register (DMASRR – write format)

DMA Software Request

(write format)

DMASRR

Expanded Addr:

ISA Addr:

Reset State:

F009H

0009H

00H

7

0

—

—

—

—

—

SR

0

CS

Bit

Number

Bit

Mnemonic

Function

7–3

—

Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

2

SR

Software Request:

Setting this bit generates a software request for the channel specified by

bit 0. When the channel’s buffer transfer completes, this bit is cleared.

1

0

Must be 0 for correct operation.

0

CS

Channel Select:

0 = The selection for bit 2 affects channel 0.

1 = The selection for bit 2 affects channel 1.