D.54 rfscir, D.55 rfscon – Intel 386 User Manual

Page 620

D-55

SYSTEM REGISTER QUICK REFERENCE

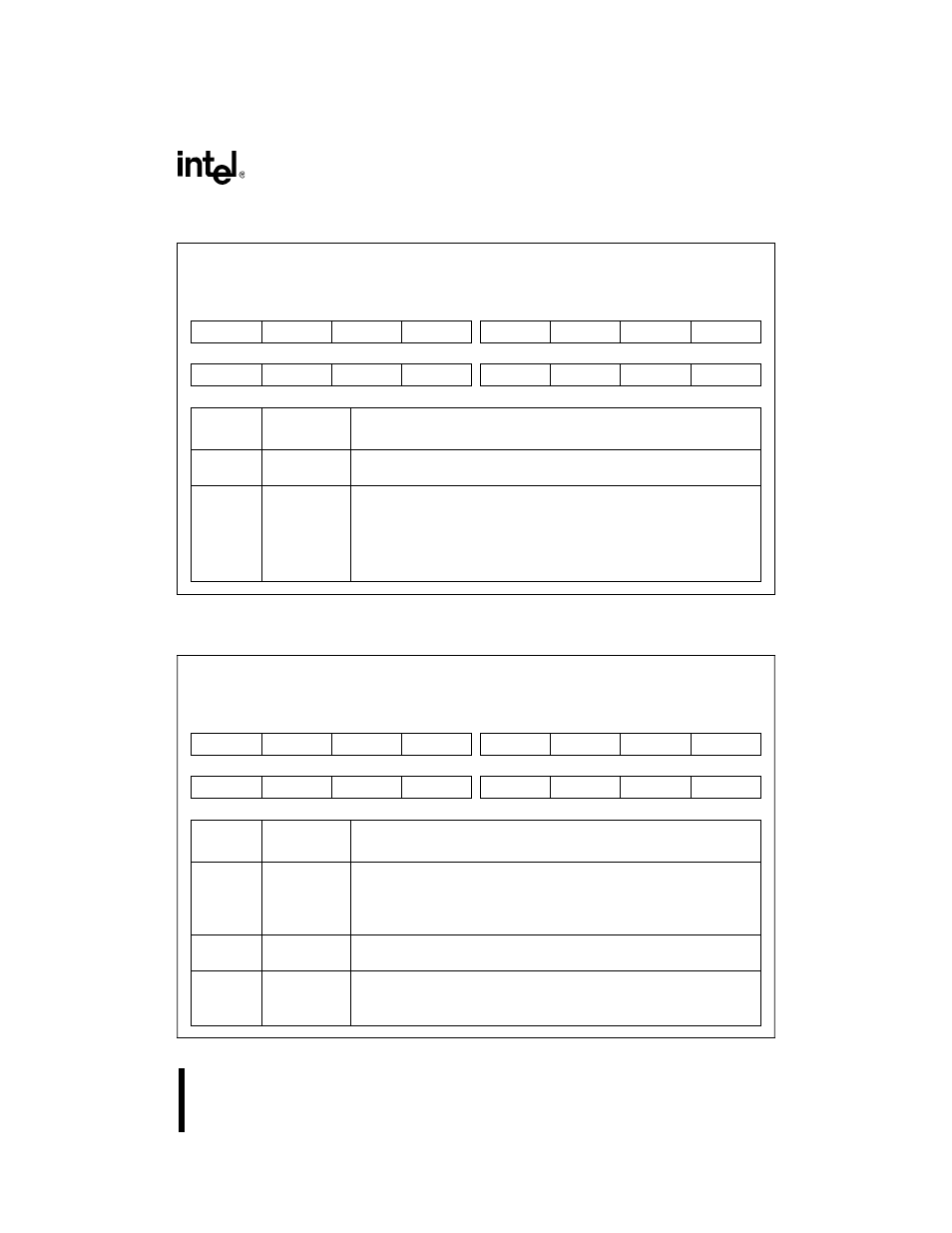

D.54 RFSCIR

D.55 RFSCON

Refresh Clock Interval

RFSCIR

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F4A2H

—

0000H

15

8

—

—

—

—

—

—

RC9

RC8

7

0

RC7

RC6

RC5

RC4

RC3

RC2

RC1

RC0

Bit

Number

Bit

Mnemonic

Function

15–10

—

Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

9–0

RC9:0

Refresh Counter Value:

Write the counter value to these ten bits. The interval counter counts

down from this value. When the interval counter reaches one, the control

unit initiates a refresh request (provided it does not have a request

pending). The counter value is a function of DRAM specifications and

processor frequency (see the equation above).

Refresh Control

RFSCON

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F4A4H

—

0000H

15

8

REN

—

—

—

—

—

CV9

CV8

7

0

CV7

CV6

CV5

CV4

CV3

CV2

CV1

CV0

Bit

Number

Bit

Mnemonic

Function

15

REN

Refresh Control Unit Enable:

This bit enables or disables the refresh control unit.

0 = Disables refresh control unit

1 = Enables refresh control unit

14–10

—

Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

9–0

CV9:0

Counter Value:

These read-only bits represent the current value of the interval counter.

Write operations to these bits have no effect.