Figure 119. port 2 configuration register (p2cfg) – Intel 386 User Manual

Page 306

11-19

ASYNCHRONOUS SERIAL I/O UNIT

Use P2CFG bits 7–5 to connect SIO0 signals to package pins.

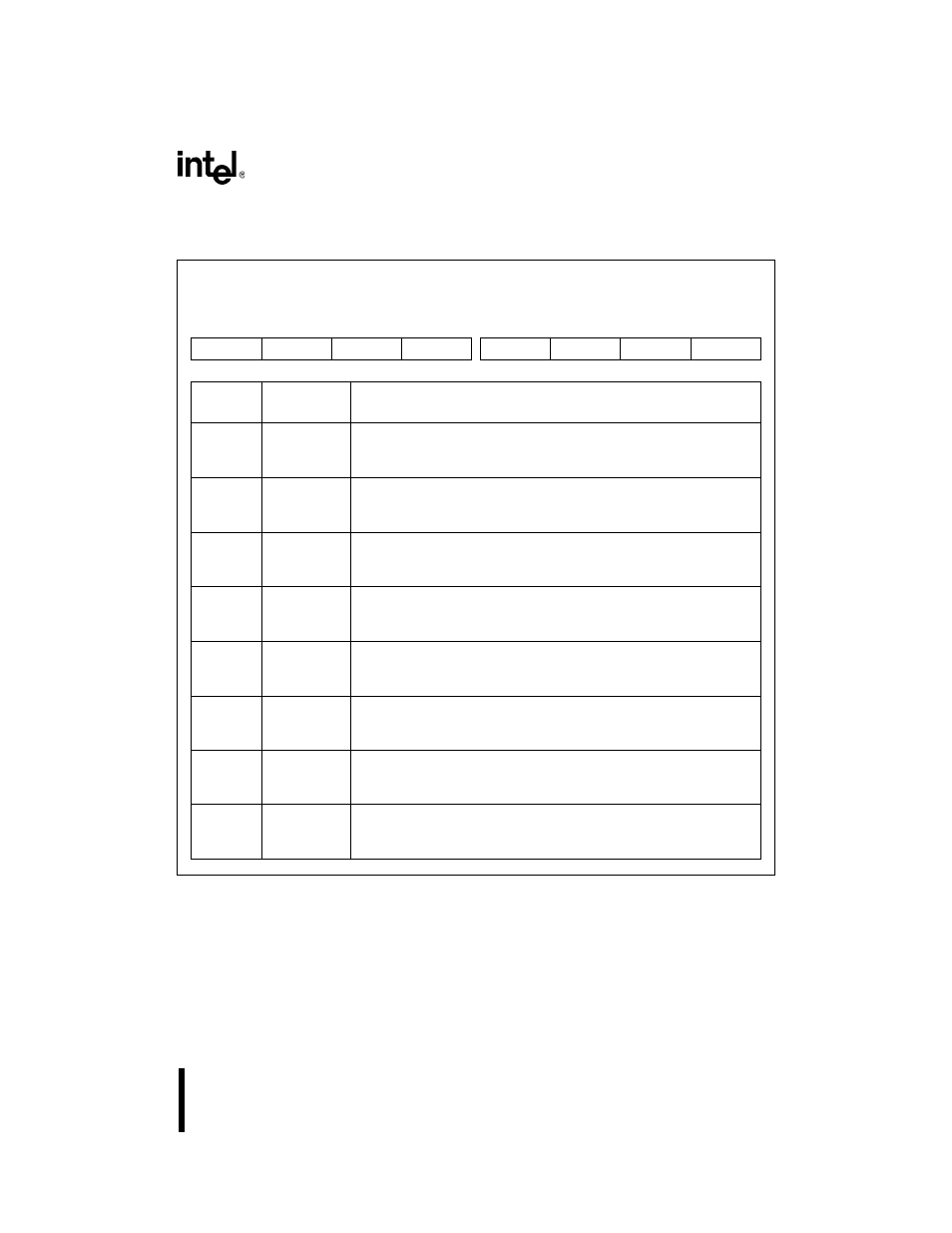

Figure 11-9. Port 2 Configuration Register (P2CFG)

Port 2 Configuration

P2CFG

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F822H

—

00H

7

0

PM7

PM6

PM5

PM4

PM3

PM2

PM1

PM0

Bit

Number

Bit

Mnemonic

Function

7

PM7

Pin Mode:

0 = Selects P2.7 at the package pin.

1 = Selects CTS0# at the package pin.

6

PM6

Pin Mode:

0 = Selects P2.6 at the package pin.

1 = Selects TXD0 at the package pin.

5

PM5

Pin Mode:

0 = Selects P2.5 at the package pin.

1 = Selects RXD0 at the package pin.

4

PM4

Pin Mode:

0 = Selects P2.4 at the package pin.

1 = Selects CS4# at the package pin.

3

PM3

Pin Mode:

0 = Selects P2.3 at the package pin.

1 = Selects CS3# at the package pin.

2

PM2

Pin Mode:

0 = Selects P2.2 at the package pin.

1 = Selects CS2# at the package pin.

1

PM1

Pin Mode:

0 = Selects P2.1 at the package pin.

1 = Selects CS1# at the package pin.

0

PM0

Pin Mode:

0 = Selects P2.0 at the package pin.

1 = Selects CS0# at the package pin.