5 receive buffer register (rbrn), Figure 1114. receive buffer register (rbrn) – Intel 386 User Manual

Page 311

Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

11-24

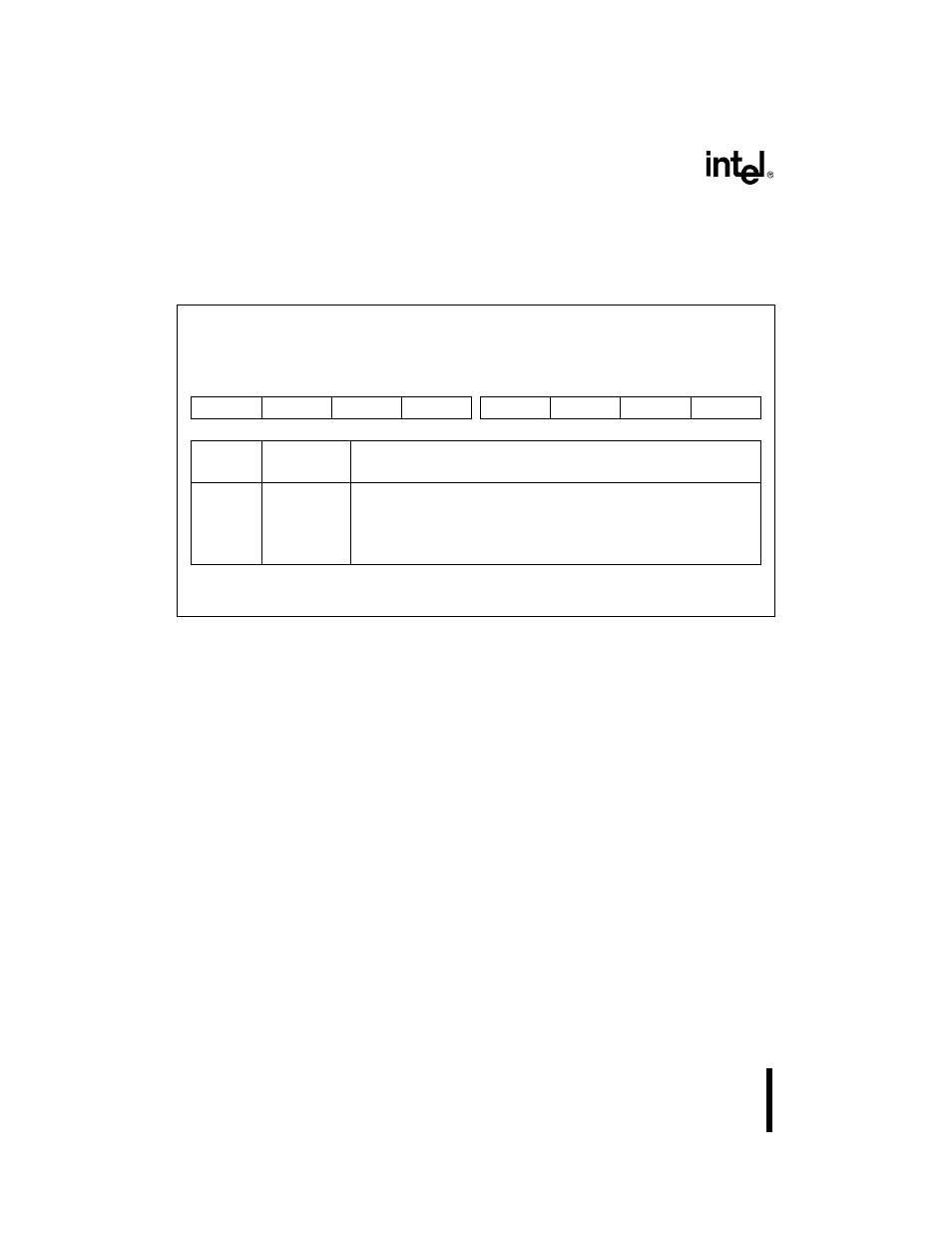

11.3.5 Receive Buffer Register (RBR

n)

Read RBRn to obtain the last data word received. Use the interrupt control or DMA units or poll

the serial line status register (LSRn) to determine whether the receive buffer is full.

Figure 11-14. Receive Buffer Register (RBR

n

)

Receive Buffer

RBR0, RBR1

(read only)

Expanded Addr:

ISA Addr:

Reset State:

RBR0

RBR1

F4F8H

F8F8H

03F8H

02F8H

XXH

XXH

7

0

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0

Bit

Number

Bit

Mnemonic

Function

7–0

RB7:0

Receive Buffer Bits:

These bits make up the last word received. The receiver shifts bits in,

starting with the least-significant-bit. The receiver then strips off the

asynchronous bits (start, parity, and stop) and transfers the received

data bits from the receive shift register to the receive buffer.

NOTE:

The receive buffer register shares an address port with other SIO registers. Bit 7 (DLAB) of

the LCR

n must be cleared in order to read the receive buffer register.