2 controlling the psclk frequency, Figure 84. clock prescale register (clkprs) – Intel 386 User Manual

Page 188

8-7

CLOCK AND POWER MANAGEMENT UNIT

8.2

CONTROLLING THE PSCLK FREQUENCY

The PSCLK signal can provide a 50% duty cycle prescaled clock to the timer/counter and SSIO

units. This feature is useful for providing various frequencies, including a 1.19318 MHz output

for a PC-compatible system timer, or speaker tone generator. Determine the required prescale val-

ue using the following formula, then write this value to the CLKPRS register (Figure 8-4).

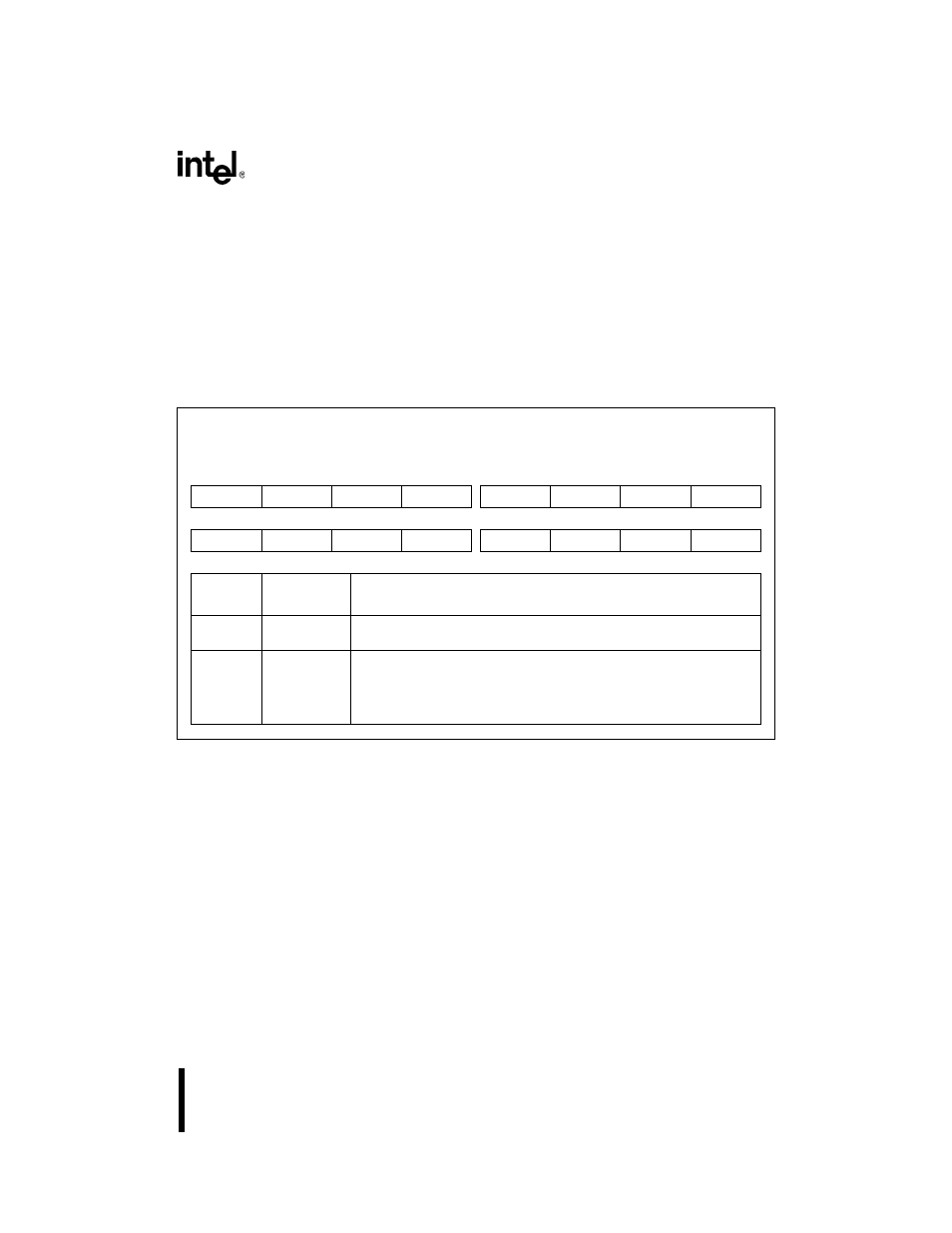

Figure 8-4. Clock Prescale Register (CLKPRS)

To change the frequency of PSCLK, write a new value to the CLKPRS register. The new frequen-

cy takes effect at the first high-to-low transition of PSCLK after CLKPRS has been changed.

Clock Prescale Register

CLKPRS

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F804H

—

0000H

15

8

—

—

—

—

—

—

—

PS8

7

0

PS7

PS6

PS5

PS4

PS3

PS2

PS1

PS0

Bit

Number

Bit

Mnemonic

Function

15–9

—

Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

8–0

PS8:0

Prescale Value:

These bits determine the divisor that is used to generate PSCLK. Legal

values are from 0000H (divide by 2) to 01FFH (divide by 513).

divisor = PS8:0 + 2

Prescale value

internal clock frequency (CLK2/2)

desired PSCLK frequency

----------------------------------------------------------------------------------------

2

–

=