14 interrupt enable register (dmaien), Figure 1233. dma interrupt enable register (dmaie – Intel 386 User Manual

Page 383

Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

12-48

12.3.14 Interrupt Enable Register (DMAIEN)

Use DMAIEN to individually connect channel 0’s and 1’s transfer complete signal to the

DMAINT interrupt request output.

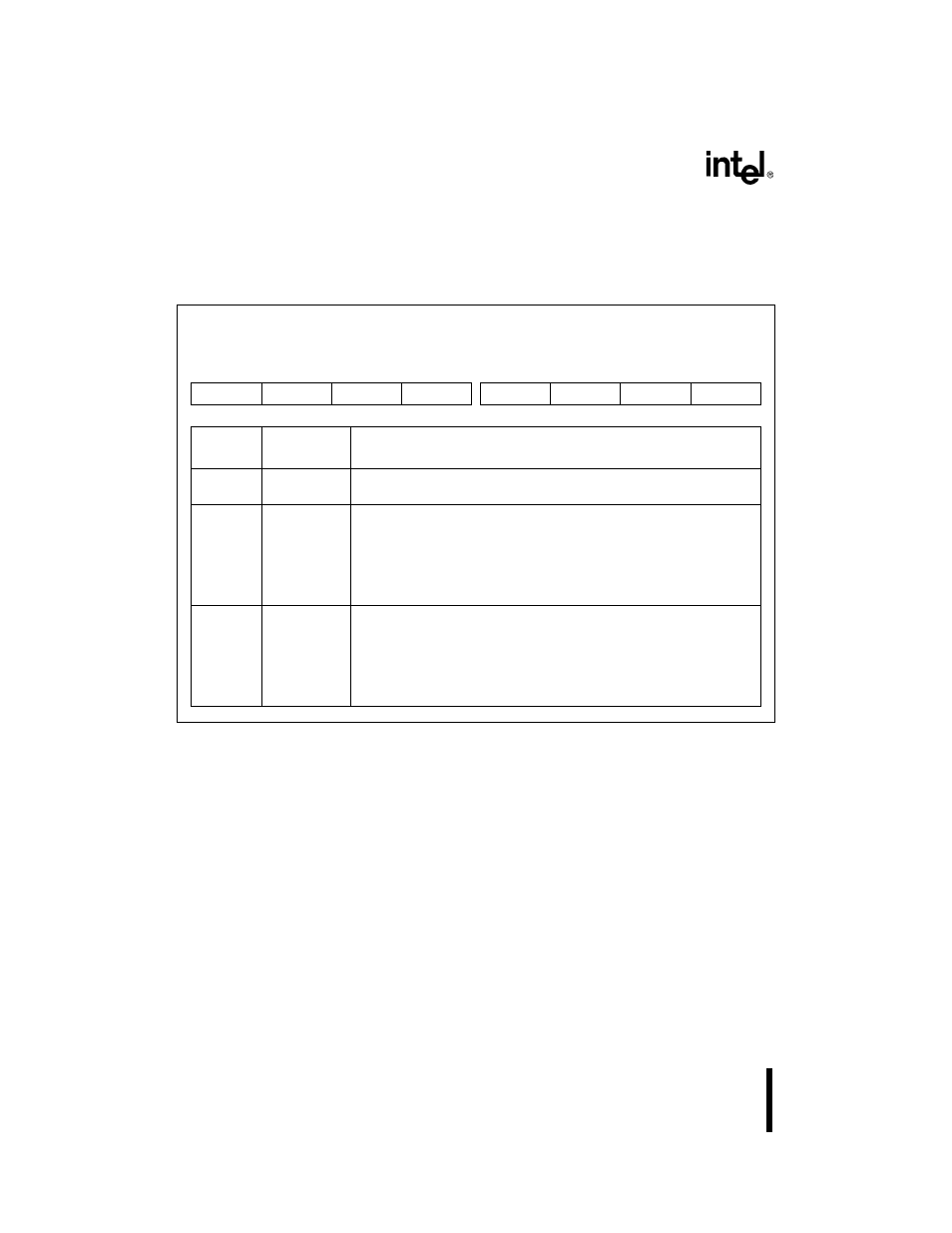

Figure 12-33. DMA Interrupt Enable Register (DMAIEN)

DMA Interrupt Enable

DMAIEN

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F01CH

—

00H

7

0

—

—

—

—

—

—

TC1

TC0

Bit

Number

Bit

Mnemonic

Function

7–2

—

Reserved. These bits are undefined; for compatibility with future devices,

do not modify these bits.

1

TC1

Transfer Complete 1:

0 = Disables Transfer Complete interrupts.

1 = Connects channel 1’s transfer complete signal to the interrupt

control unit’s DMAINT input.

Note: When channel 1 is in chaining mode (DMACHR.2=1 and

DMACHR.0=1), this bit is a don’t care.

0

TC0

Transfer Complete 0:

0 = Disables Transfer Complete interrupts.

1 = Connects channel 0’s transfer complete signal to the interrupt

control unit’s DMAINT input.

Note: When channel 0 is in chaining mode (DMACHR.2=1 and

DMACHR.0=0), this bit is a don’t care.