Figure 1023. port 3 configuration register (p3cfg – Intel 386 User Manual

Page 265

Intel386™ EX EMBEDDED PROCESSOR USER’S MANUAL

10-22

The peripheral pin selection registers (P3CFG and PINCFG) determine whether each counter’s

OUTn signal is connected to its TMROUTn pin. See Figure 10-1 for the TCU signal connections.

For details on the P3CFG and PINCFG registers see Figure 10-23 and Figure 10-24. The counter

output signals are automatically connected to the interrupt control unit. Counter 1’s output signal

(OUT1) is automatically connected to DMA channel 0, and counter 2’s output signal (OUT2) is

automatically connected to DMA channel 1.

Use P3CFG bits 0 and 1 to connect TMROUT0 and TMROUT1 to package pins.

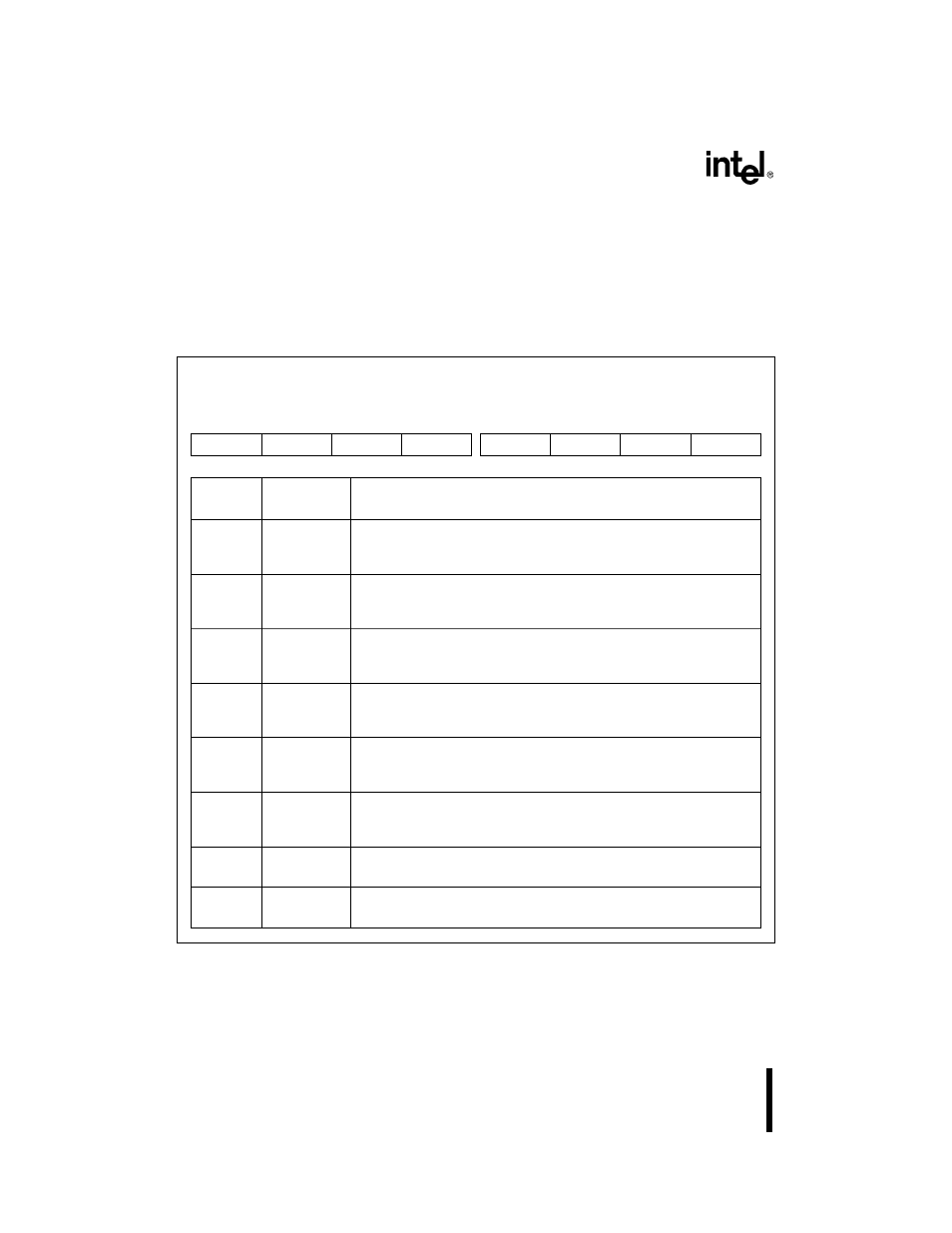

Figure 10-23. Port 3 Configuration Register (P3CFG)

Port 3 Configuration

P3CFG

(read/write)

Expanded Addr:

ISA Addr:

Reset State:

F824H

—

00H

7

0

PM7

PM6

PM5

PM4

PM3

PM2

PM1

PM0

Bit

Number

Bit

Mnemonic

Function

7

PM7

Pin Mode:

0 = Selects P3.7 at the package pin.

1 = Selects COMCLK at the package pin.

6

PM6

Pin Mode:

0 = Selects P3.6 at the package pin.

1 = Selects PWRDOWN at the package pin.

5

PM5

Pin Mode:

0 = Selects P3.5 at the package pin.

1 = Connects master IR7 to the package pin (INT3).

4

PM4

Pin Mode:

0 = Selects P3.4 at the package pin.

1 = Connects master IR6 to the package pin (INT2).

3

PM3

Pin Mode:

0 = Selects P3.3 at the package pin.

1 = Connects master IR5 to the package pin (INT1).

2

PM2

Pin Mode:

0 = Selects P3.2 at the package pin.

1 = Connects master IR1 to the package pin (INT0).

1

PM1

Pin Mode:

See Table 5-1 on page 5-8 for all the PM1 configuration options.

0

PM0

Pin Mode:

See Table 5-1 on page 5-8 for all the PM0 configuration options.